Crédit :Samsung

"Le processus nanométrique traite de l'espace entre les transistors montés sur un substrat à un niveau nanométrique, " mentionné Impulsion .

« Plus la distance est étroite, plus vous pouvez insérer de puces pour augmenter la puissance de calcul et l'efficacité énergétique. Un nanomètre correspond à un dix millième du diamètre d'un cheveu humain."

Au Samsung Foundry Forum à Santa Clara, Californie, la société a récemment cherché à impressionner les progrès réalisés dans le développement de processus 3 nm gate-all-around (GAA).

Samsung Foundry présente maintenant MBCFET (FET à canaux multiples). Il s'agit de nanofeuillets multi-empilés. Avec la formation de nanofeuillets, un courant plus important par pile est réalisable, mentionné SamMobile .

Technologie extrême a décrit l'annonce comme étant « une nouvelle, architecture de transistor évoluée" provenant de Samsung Foundry, impliquant l'approche "nanosheets" pour son nœud 3 nm.

(De la salle de rédaction de Samsung : « La GAA conventionnelle basée sur les nanofils nécessite un plus grand nombre de piles en raison de sa faible largeur de canal efficace. D'autre part, La version brevetée de Samsung de GAA, MBCFET (FET multi-ponts-canaux), utilise une architecture de nanofeuilles, permettant un plus grand courant par pile.")

Le blog CNXSoft a également expliqué pourquoi la transition des nanofils aux nanofeuilles.

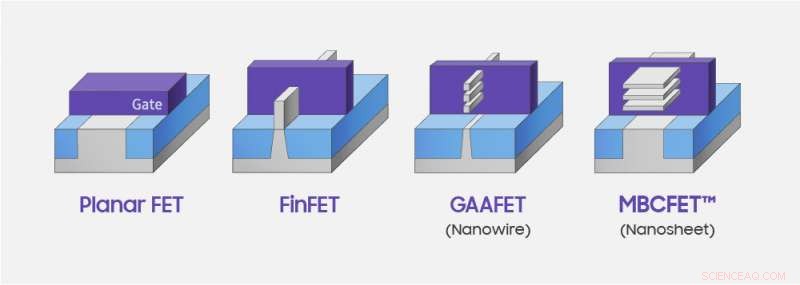

"Nous lisons souvent que les nouveaux processeurs sont fabriqués avec un processus FinFET. Le nouveau processus a été créé en raison des effets de canal court dans les transistors planaires traditionnels, et FinFET (transistor à effet de champ Fin) a été introduit pour permettre une mise à l'échelle de la tension supplémentaire, mais le nœud de processus devenant de plus en plus petit, les effets électrostatiques ont commencé à poser problème."

L'utilisation de nanofils GAA (Gate All Around) pour limiter ces effets a été prise comme réponse, mais ceux-ci sont apparemment très difficiles à intégrer dans le silicium, dit le blog, Samsung a donc fini par utiliser des couches minces (nanosheets) au lieu de nanofils, "permettant un plus grand courant par piste dans leur implémentation GAA appelée MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

Pour ceux qui ont besoin de traiter la surcharge d'acronymes, Ramish Zafar dans WCcftech a emmené ses lecteurs tout au long du voyage Samsung. 1. Samsung a collaboré avec IBM pour les nœuds de processus GAAFET (Gate-All-Around). 2. Maintenant, la société a annoncé ses personnalisations par rapport au processus précédent, et c'est MBCFET.

Zafar avait plus à dire sur MBCET. "Contrairement aux conceptions FinFET traditionnelles, GAAFET permet au matériau de la grille d'entourer le canal de tous les côtés. Samsung affirme que la conception de MBCFET améliorera le comportement marche-arrêt du processus, et permettre aux processeurs de réduire la tension de fonctionnement en dessous de 0,75 V. Un point crucial pour MBCFET est que le processus est entièrement compatible avec les conceptions FinFET et ne nécessite aucun nouvel outil pour la fabrication. »

Crédit :Samsung

Comment, bien que, est-ce que toutes ces bonnes nouvelles figurent dans les plans de développement de l'entreprise. Quand pouvons-nous nous attendre à voir la technologie en action ? Joel Hruska a abordé cette question dans Technologie extrême .

« Lors de son Samsung Foundry Forum cette semaine, Samsung a déclaré que son Product Design Kit pour puces 3nm est désormais en alpha, ayant atteint le jalon de développement 0,1. Samsung prévoit de lancer une pléthore de nœuds de processus dans les années à venir, avec des pistes de développement prévues en 7nm, 6 nm, 5 nm, 4 nm, et oui, 3 nm."

Hruska a ajouté, "Les améliorations pour 3 nm par rapport à 7 nm sont assez bonnes, mais ce nœud ne sera pas expédié avant un certain temps. » Son article contient un graphique qui montre la progression communiquée par Samsung.

© 2019 Réseau Science X