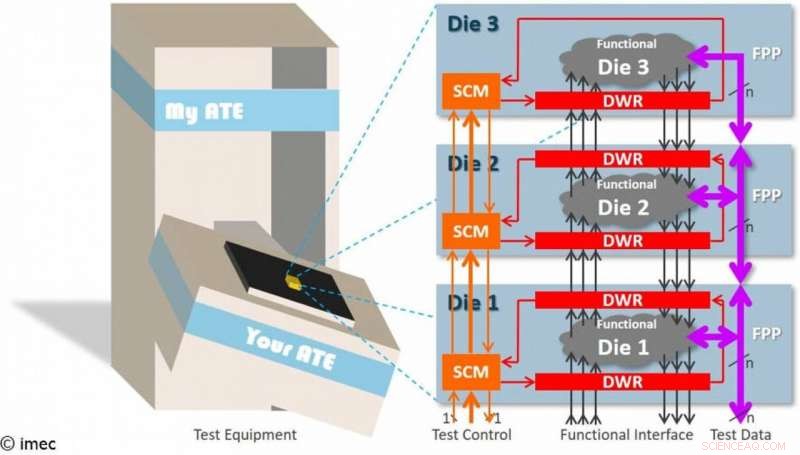

Coupe transversale conceptuelle d'un CI 3D composé de trois matrices empilées. L'équipement de test envoie des stimuli de test et reçoit des réponses de test de l'interface externe du 3D-IC située au bas de la pile. Les éléments de conception pour le test IEEE Std 1838™-2019 dans les différentes puces forment une architecture d'accès aux tests cohérente grâce à laquelle l'équipement de test peut accéder à chaque puce de la pile. Crédit :IMEC

Cette semaine, IMEC, un pôle de recherche et d'innovation de premier plan dans le domaine de la nanoélectronique et des technologies numériques, a annoncé que IEEE Std 1838TM-2019—récemment approuvé par l'IEEE Standards Association—sera inclus dans la bibliothèque numérique IEEE Xplore à partir de février 2020. La nouvelle norme permet aux fabricants de matrices de concevoir des matrices qui, si conforme à cette norme, constituer, une fois empilé dans un 3-D-IC par un intégrateur de pile, une architecture d'accès aux tests cohérente au niveau de la pile. L'effort de standardisation du 3-D-DfT (design-for-test) a été initié par l'IMEC.

Les circuits intégrés 3-D exploitent la dimension verticale pour une intégration plus poussée en empilant les matrices les unes sur les autres afin de maintenir l'élan de la loi de Moore. Eric Beyne, boursier et directeur de programme 3-D System Integration à IMEC, dit, « Les progrès des technologies de traitement des plaquettes et d'assemblage d'empilements créent une multitude d'architectures d'empilement différentes. Cela entraîne une forte augmentation du nombre de moments potentiels auxquels les tests de défauts de fabrication peuvent être exécutés :pré-collage (avant empilement), mid-bond (sur stacks partiels), post-bond (sur piles complètes), et test final (sur les circuits intégrés 3-D emballés). L'équipement de test contacte les circuits intégrés via son interface externe via des aiguilles de sonde ou au niveau de la prise de test. Dans une pile de dés, cette interface externe réside généralement dans la matrice inférieure de la pile. Pour que l'équipement de test soit capable de fournir des stimuli de test et de recevoir des réponses des différents matrices de la pile, la collaboration des matrices sous-jacentes est nécessaire pour fournir un accès de test à la matrice actuellement testée."

Un groupe de travail IEEE pour standardiser 3-D-DfT a été fondé en 2011 par Erik Jan Marinissen, directeur scientifique de l'IMEC à Louvain, Belgique et il en a été le premier président. Dans les années récentes, Adam Cron, ingénieur principal R&D au sein du groupe de conception de Synopsys, a été la force motrice en tant que président actuel du groupe de travail.

Amit Sanghani, vice-président de l'ingénierie dans le groupe de conception chez Synopsys à Mountain View, Californie, Les États-Unis ont déclaré :« Le 3-D-IC est une technologie importante pour fournir la prochaine vague d'innovation alors que l'industrie dépasse les 7 nm. Actuellement, die peut provenir de différents fournisseurs avec des architectures DfT disjointes.

La nouvelle norme se compose de trois éléments principaux. (1) DWR, le registre d'enveloppe de puces :des chaînes de balayage à la limite de chaque puce dans la pile pour permettre un test modulaire des internes de chaque puce et des interconnexions entre chaque paire de puces adjacentes. (2) SCM, le mécanisme de contrôle série :un mécanisme de contrôle de test à un seul bit qui transporte des instructions dans la pile pour contrôler les modes de test des différentes enveloppes de matrice. (3) FPP, le port parallèle flexible en option, c'est à dire., un mécanisme d'accès aux tests multi-bits évolutif pour transporter efficacement vers le haut et vers le bas de la pile de matrices les gros volumes de données généralement associés aux tests de production. Alors que DWR et SCM sont basés sur les normes DfT existantes, le FPP est vraiment nouveau par rapport à IEEE Std 1838.

Wolfgang Meyer, directeur de groupe senior R&D chez Cadence Design Systems à San Jose, Californie, NOUS., dit, "Une norme DfT comme IEEE Std 1838 est importante pour l'industrie. Les fabricants de matrices savent ce qu'ils doivent fournir, et les intégrateurs de piles savent à quoi ils peuvent s'attendre. De plus, Les fournisseurs d'EDA comme Cadence peuvent concentrer leur support d'outils sur des architectures conformes à la nouvelle norme. Il est bon qu'il y ait une certaine évolutivité définie par l'utilisateur avec la norme car le champ 3-D-IC est si large qu'une norme rigide « taille unique » ne fonctionnerait pas. »

Junlin Huang, manager d'une équipe DfT forte de 150 personnes de HiSilicon à Shenzhen, Chine, dit, "Par an, nous réalisons l'insertion DfT et la génération automatique de modèles de test (ATPG) pour des dizaines de conceptions de puces numériques très grandes et complexes dans les technologies les plus avancées. Maintenant, ces produits commencent à utiliser la technologie 3D et mon équipe DfT doit être prête à relever les défis DfT et ATPG associés. IEEE Std 1838 nous aidera dans cette tâche."

A partir de février 2020, la nouvelle norme IEEE Std 1838 sera disponible via IEEE Xplore pour les abonnés aux normes IEEE ainsi qu'à l'achat pour tout le monde.