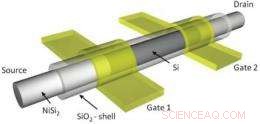

Le noyau du transistor reconfigurable est constitué d'une structure de nanofils intégrée dans une coque en dioxyde de silicium. Des électrons ou des trous s'écoulent de la source à une extrémité du nanofil à travers deux grilles jusqu'au drain à l'autre extrémité du nanofil. Une porte est utilisée pour programmer la polarité p ou n, tandis que l'autre porte règle la conductance à travers le nanofil. Crédit image : ©Namlab gGmbH

(PhysOrg.com) -- La plupart des appareils électroniques actuels contiennent deux types différents de transistors à effet de champ (FET) :le type n (qui utilise des électrons comme porteurs de charge) et le type p (qui utilise des trous). Généralement, un transistor ne peut être que d'un type ou de l'autre, mais pas les deux. Maintenant dans une nouvelle étude, les chercheurs ont conçu un transistor qui peut se reconfigurer en tant que type n ou type p lorsqu'il est programmé par un signal électrique. Un ensemble de ces « transistors universels » peut, en principe, effectuer n'importe quelle opération de logique booléenne, ce qui signifie que les circuits pourraient exécuter le même nombre de fonctions logiques avec moins de transistors. Cet avantage pourrait conduire à un matériel plus compact et à de nouvelles conceptions de circuits.

Les chercheurs qui ont conçu le transistor, dirigé par Walter M. Weber chez Namlab gGmbH à Dresde, Allemagne, ont publié le nouveau concept dans un récent numéro de Lettres nano .

« Des nanofils synthétiques sont utilisés pour réaliser la preuve de principe, " Weber a dit PhysOrg.com . "Toutefois, le concept est entièrement transférable à la technologie de pointe du silicium CMOS et peut utiliser des processus auto-alignés.

Le noyau du nouveau transistor est constitué d'un seul nanofil constitué d'une structure métal-semi-conducteur-métal, qui est noyé dans une coque en dioxyde de silicium. Des électrons ou des trous s'écoulent de la source à une extrémité du nanofil à travers deux grilles jusqu'au drain à l'autre extrémité du nanofil. Les deux portes contrôlent le flux d'électrons ou de trous de différentes manières. Une grille sélectionne le type de transistor en choisissant d'utiliser soit des électrons, soit des trous, tandis que l'autre porte contrôle les électrons ou les trous en réglant la conductance du nanofil.

L'utilisation d'une grille pour sélectionner la configuration de type p ou n est assez différente des transistors conventionnels. Dans les transistors conventionnels, le fonctionnement de type p ou n résulte du dopage qui se produit pendant le processus de fabrication, et ne peut pas être changé une fois le transistor fabriqué. En revanche, le transistor reconfigurable n'utilise aucun dopage. Au lieu, une tension externe appliquée à une grille peut reconfigurer le type de transistor même pendant le fonctionnement. La tension fait que la jonction Schottky près de la grille empêche les électrons ou les trous de traverser le dispositif. Donc si les électrons sont bloqués, les trous peuvent s'écouler et le transistor est de type p. En appliquant une tension légèrement différente, la reconfiguration peut être à nouveau commutée, sans gêner le flux.

Les scientifiques expliquent que la clé pour faire fonctionner cette reconfiguration est la capacité de régler le transport électronique à travers chacune des deux jonctions (une par porte) séparément. Leurs simulations ont montré que le courant est dominé par l'effet tunnel, suggérant que la géométrie des nanofils joue un rôle important dans la capacité de contrôle indépendant des jonctions.

Étant donné que le transistor reconfigurable peut exécuter les fonctions logiques des FET de type p et n, un seul transistor pourrait remplacer à la fois un FET de type p et n dans un circuit, ce qui réduirait considérablement la taille du circuit sans réduire la fonctionnalité. Même à ce stade précoce, le transistor reconfigurable présente de très bonnes caractéristiques électriques, y compris un rapport marche/arrêt record et un courant de fuite réduit par rapport aux FET à nanofils conventionnels. À l'avenir, les chercheurs prévoient d'améliorer encore les performances du transistor.

« Nous varions les combinaisons de matériaux pour améliorer encore les performances de l'appareil, ", a déclaré Weber. "Plus loin, les premiers circuits mettant en œuvre ces dispositifs sont en cours de construction. … Le plus grand défi sera d'incorporer les signaux de grille supplémentaires dans la disposition des cellules permettant une interconnexion flexible avec les autres transistors.

Copyright 2011 PhysOrg.com.

Tous les droits sont réservés. Ce matériel ne peut pas être publié, diffuser, réécrit ou redistribué en tout ou en partie sans l'autorisation écrite expresse de PhysOrg.com.