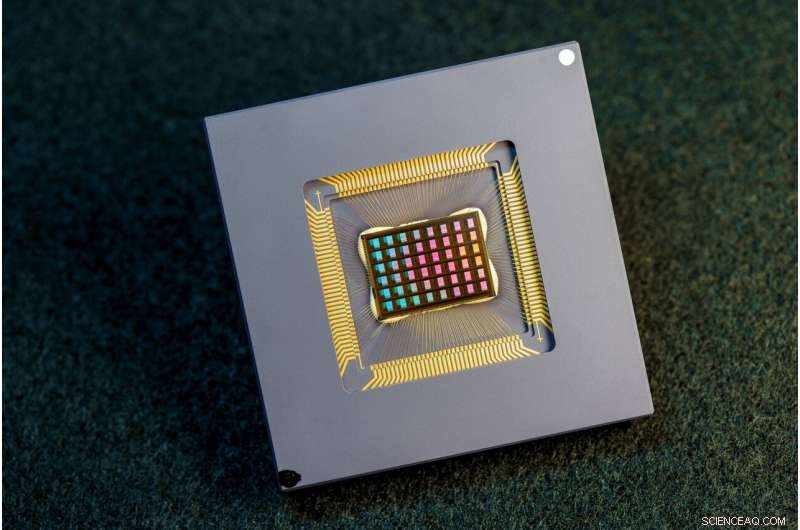

Une équipe de chercheurs internationaux a conçu, fabriqué et testé la puce NeuRRAM. Crédit :David Baillot/Université de Californie à San Diego

Une équipe internationale de chercheurs a conçu et construit une puce qui exécute des calculs directement en mémoire et peut exécuter une grande variété d'applications d'IA, le tout à une fraction de l'énergie consommée par les plates-formes informatiques pour l'informatique d'IA à usage général.

La puce neuromorphique NeuRRAM rapproche l'IA de son exécution sur une large gamme d'appareils périphériques, déconnectés du cloud, où ils peuvent effectuer des tâches cognitives sophistiquées n'importe où et n'importe quand sans dépendre d'une connexion réseau à un serveur centralisé. Les applications abondent aux quatre coins du monde et dans toutes les facettes de notre vie, et vont des montres intelligentes aux casques de réalité virtuelle, en passant par les écouteurs intelligents, les capteurs intelligents dans les usines et les rovers pour l'exploration spatiale.

La puce NeuRRAM n'est pas seulement deux fois plus économe en énergie que les puces "compute-in-memory" à la pointe de la technologie, une classe innovante de puces hybrides qui exécutent des calculs en mémoire, elle fournit également des résultats aussi précis que puces numériques conventionnelles. Les plates-formes d'IA conventionnelles sont beaucoup plus volumineuses et sont généralement contraintes d'utiliser de grands serveurs de données fonctionnant dans le cloud.

De plus, la puce NeuRRAM est très polyvalente et prend en charge de nombreux modèles et architectures de réseaux neuronaux différents. En conséquence, la puce peut être utilisée pour de nombreuses applications différentes, y compris la reconnaissance et la reconstruction d'images ainsi que la reconnaissance vocale.

"La sagesse conventionnelle est que l'efficacité supérieure du calcul en mémoire se fait au détriment de la polyvalence, mais notre puce NeuRRAM obtient l'efficacité sans sacrifier la polyvalence", a déclaré Weier Wan, le premier auteur correspondant de l'article et un récent doctorat. diplômé de l'Université de Stanford qui a travaillé sur la puce à l'UC San Diego, où il a été co-dirigé par Gert Cauwenberghs au Département de bioingénierie.

L'équipe de recherche, co-dirigée par des bioingénieurs de l'Université de Californie à San Diego, présente ses résultats dans le numéro du 17 août de Nature .

Actuellement, l'IA informatique est à la fois gourmande en énergie et coûteuse en calcul. La plupart des applications d'IA sur les appareils périphériques impliquent le déplacement des données des appareils vers le cloud, où l'IA les traite et les analyse. Ensuite, les résultats sont transférés vers l'appareil. En effet, la plupart des appareils de périphérie sont alimentés par batterie et, par conséquent, ne disposent que d'une quantité limitée d'énergie pouvant être dédiée à l'informatique.

En réduisant la consommation d'énergie nécessaire à l'inférence de l'IA à la périphérie, cette puce NeuRRAM pourrait conduire à des dispositifs de périphérie plus robustes, plus intelligents et accessibles et à une fabrication plus intelligente. Cela pourrait également conduire à une meilleure confidentialité des données, car le transfert de données des appareils vers le cloud s'accompagne de risques de sécurité accrus.

Sur les puces AI, le déplacement des données de la mémoire vers les unités de calcul est un goulot d'étranglement majeur.

"C'est l'équivalent d'un trajet de huit heures pour une journée de travail de deux heures", a déclaré Wan.

Pour résoudre ce problème de transfert de données, les chercheurs ont utilisé ce que l'on appelle la mémoire résistive à accès aléatoire, un type de mémoire non volatile qui permet le calcul directement dans la mémoire plutôt que dans des unités de calcul séparées. La RRAM et d'autres technologies de mémoire émergentes utilisées comme matrices de synapses pour l'informatique neuromorphique ont été mises au point dans le laboratoire de Philip Wong, conseiller de Wan à Stanford et principal contributeur à ce travail. Le calcul avec des puces RRAM n'est pas forcément nouveau, mais il conduit généralement à une diminution de la précision des calculs effectués sur la puce et à un manque de flexibilité dans l'architecture de la puce.

"Le calcul en mémoire est une pratique courante dans l'ingénierie neuromorphique depuis son introduction il y a plus de 30 ans", a déclaré Cauwenberghs. « Ce qui est nouveau avec NeuRRAM, c'est que l'efficacité extrême s'accompagne désormais d'une grande flexibilité pour diverses applications d'IA, avec presque aucune perte de précision par rapport aux plates-formes de calcul numériques standard à usage général. »

Une méthodologie soigneusement élaborée était la clé du travail avec plusieurs niveaux de "co-optimisation" à travers les couches d'abstraction du matériel et des logiciels, de la conception de la puce à sa configuration pour exécuter diverses tâches d'IA. De plus, l'équipe s'est assurée de tenir compte de diverses contraintes allant de la physique des dispositifs de mémoire aux circuits et à l'architecture du réseau.

"Cette puce nous fournit désormais une plate-forme pour résoudre ces problèmes à travers la pile, des appareils et circuits aux algorithmes", a déclaré Siddharth Joshi, professeur adjoint d'informatique et d'ingénierie à l'Université de Notre Dame, qui a commencé à travailler sur le projet en tant que un doctorat étudiant et chercheur postdoctoral au laboratoire de Cauwenbergh à l'UC San Diego.

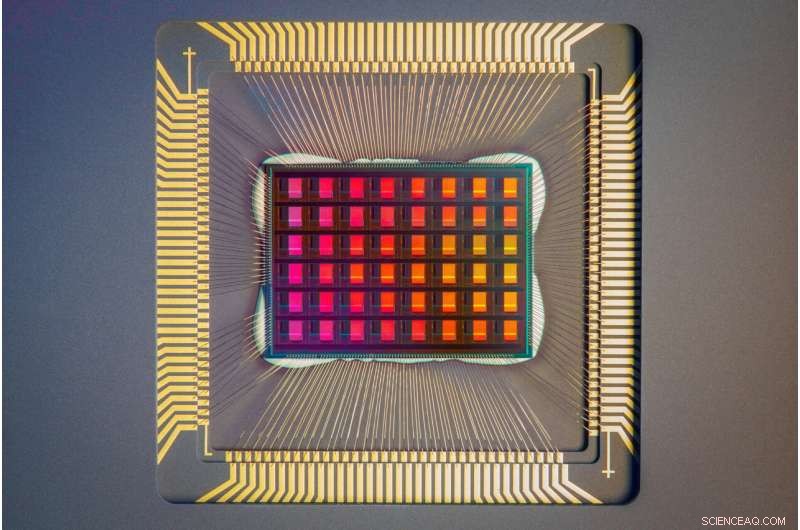

Un gros plan de la puce NeuRRAM. Crédit :David Baillot/Université de Californie à San Diego

Performance de la puce

Les chercheurs ont mesuré l'efficacité énergétique de la puce par une mesure connue sous le nom de produit à retard énergétique, ou EDP. L'EDP combine à la fois la quantité d'énergie consommée pour chaque opération et le temps nécessaire pour terminer l'opération. Par cette mesure, la puce NeuRRAM atteint un EDP 1,6 à 2,3 fois plus faible (moins c'est mieux) et une densité de calcul 7 à 13 fois plus élevée que les puces à la pointe de la technologie.

Les chercheurs ont exécuté diverses tâches d'IA sur la puce. Il a atteint une précision de 99 % sur une tâche de reconnaissance de chiffres manuscrits ; 85,7 % sur une tâche de classification d'images ; et 84,7 % sur une tâche de reconnaissance de commandes vocales Google. En outre, la puce a également permis de réduire de 70 % l'erreur de reconstruction d'image lors d'une tâche de récupération d'image. Ces résultats sont comparables aux puces numériques existantes qui effectuent des calculs avec la même précision au bit près, mais avec des économies d'énergie drastiques.

Les chercheurs soulignent que l'une des principales contributions de l'article est que tous les résultats présentés sont obtenus directement sur le matériel. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

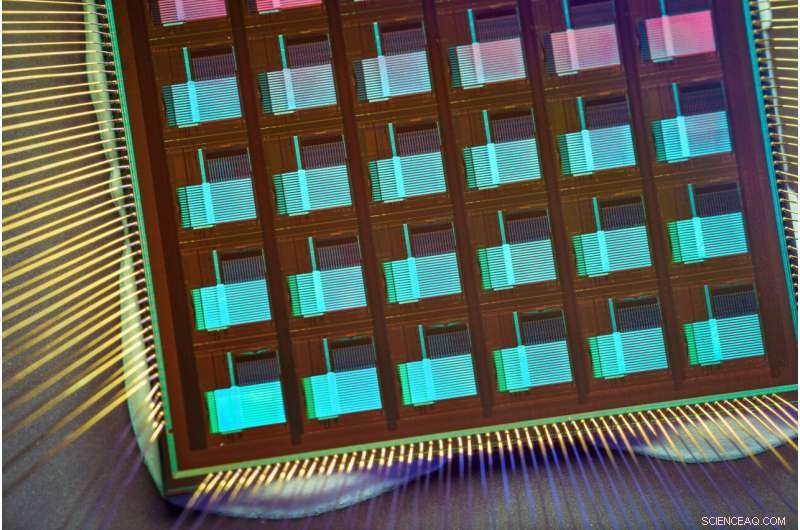

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. Une macro nvCIM de quatre mégabits pour les appareils d'intelligence artificielle de périphérie