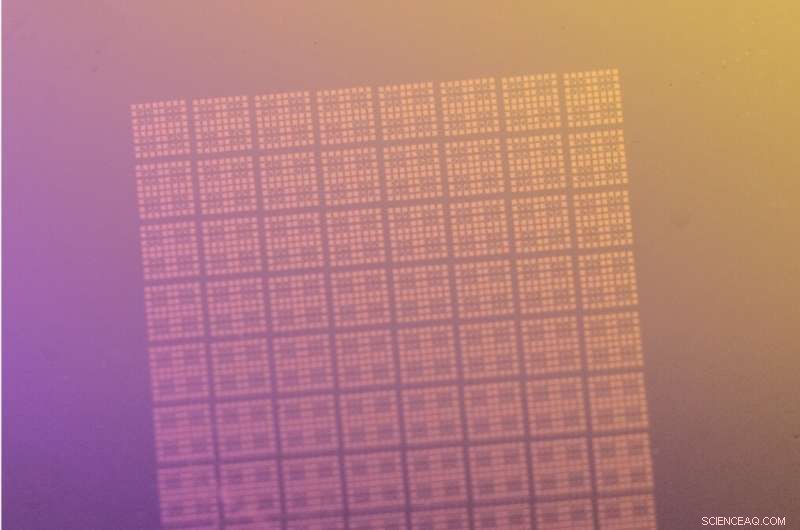

Image d'un réseau d'appareils fabriqué selon la méthode proposée par les chercheurs. Crédit :Li et al.

Les semi-conducteurs 2D pourraient avoir des applications très utiles, en particulier comme matériaux de canal pour les transistors de faible puissance. Ces matériaux présentent une très grande mobilité à des épaisseurs extrêmes, ce qui en fait des alternatives particulièrement prometteuses au silicium dans la fabrication de l'électronique.

Malgré leurs avantages, la mise en œuvre de ces matériaux dans des transistors s'est jusqu'à présent avérée difficile. En réalité, Les semi-conducteurs 2-D sont de nature sans liaison pendante; Donc, il est notoirement difficile de déposer des diélectriques de grille ultrafins à élevé (c'est-à-dire, substances à propriétés diélectriques ou isolants) sur les matériaux par dépôt de couche atomique (ALD), aboutissant souvent à des films discontinus.

Des chercheurs de l'Université de Nanjing en Chine ont récemment présenté une nouvelle stratégie pour surmonter cette limitation, permettant à terme le dépôt de diélectriques de grille sur des semi-conducteurs 2D. Dans un article publié en Nature Électronique , ils ont signalé le succès de l'ALD de diélectriques de grille à κ élevé sur des semi-conducteurs 2D en utilisant un cristal moléculaire comme couche d'ensemencement.

"Nos recherches tentent de résoudre le problème de l'intégration diélectrique de grille de haute qualité pour les transistors 2D, " Xinran Wang, l'un des chercheurs qui a mené l'étude, a déclaré TechXplore. "Dans les transistors Si de pointe, l'épaisseur effective d'oxyde (EOT) a été réduite à moins de 1 nm. Maintenant, il y a un grand écart entre les matériaux 2-D et Si en termes d'EOT, densité d'état de l'interface (Dit), et fuite de porte. Si l'on veut sérieusement faire avancer la technologie des transistors 2D, cet écart doit être comblé."

L'approche introduite par Wang et ses collègues permet la production de diélectriques avec une épaisseur d'oxyde équivalente de 1 nm sur graphène, bisulfure de molybdène (MoS

"Autre que les transistors 2-D, une autre direction explorée par mon groupe de recherche est l'électronique organique, " Wang a ajouté. " Au cours des dernières années, nous avons développé des moyens de contrôler avec précision l'assemblage des molécules sur la surface d'un matériau 2D. Pour de nombreuses molécules, y compris PTCDA, nous avons prouvé que nous pouvons contrôler la croissance si bien que seule une monocouche (~0,3 nm) est uniformément déposée, avec une interface très propre."

La couche d'interface créée par Wang et son équipe de recherche dans leurs travaux précédents est l'une des couches d'interface les plus fines actuellement réalisables. Dans leur présente étude, ils ont utilisé cette couche pour fabriquer des transistors radiofréquence au graphène qui fonctionnent à 60 GHz, ainsi que MoS

"Je pense que notre résultat le plus significatif a été que nous avons pu atteindre 1 nm d'EOT dans des matériaux 2D, " a déclaré Wang. " Il est largement admis que le canal 2-D peut réduire la consommation d'énergie des transistors par rapport aux semi-conducteurs en vrac. Cependant, pour y parvenir, nous devons utiliser la même tension de fonctionnement, et les transistors peuvent être coupés brusquement (oscillation sous le seuil proche de 60 mV/déc). Les deux quantités dépendent fortement de la qualité et de l'épaisseur du diélectrique de grille. Notre étude démontre vraiment le potentiel des semi-conducteurs 2D vers l'électronique de faible puissance."

Wang et son groupe de recherche ont été les premiers à développer avec succès des transistors 2D avec un EOT de 1 nm, déposer avec succès du diélectrique sur trois matériaux différents. Remarquablement, l'EOT et la fuite de grille qu'ils ont atteints sont comparables à ceux observés dans les CMOS au silicium de pointe, ce qui constitue une avancée significative dans ce domaine de recherche.

"Je pense qu'il y a encore beaucoup de place pour l'amélioration, " a dit Wang. " Par exemple, Le Dit dans les transistors 2-D est toujours supérieur d'environ 2 ordres de grandeur à celui du Si CMOS. En outre, ce serait formidable de réduire davantage l'EOT à ~ 0,8 nm en utilisant des oxydes à k plus élevé. Finalement, la compatibilité des matériaux que nous avons développés avec les procédés CMOS existants reste également à étudier."

© 2020 Réseau Science X