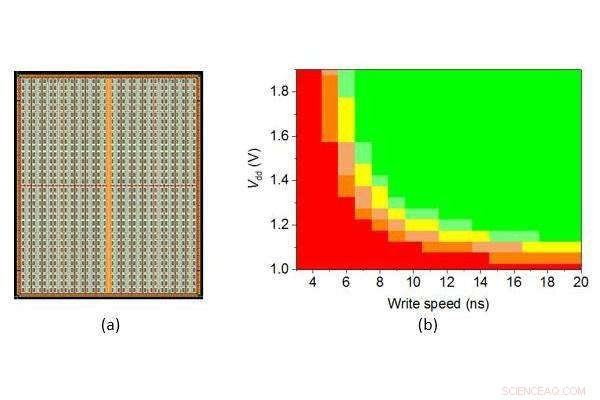

(a) Maquette d'image de STT-MRAM de densité 128 Mbit. (b) Graphique de Shmoo pour la vitesse d'écriture en fonction de la tension d'alimentation, qui montre le débit binaire de fonctionnement mesuré à chaque vitesse et tension en dégradé de couleurs. Crédit :Université du Tohoku

Une équipe de recherche, dirigé par le professeur Tetsuo Endoh à l'université de Tohoku, a développé avec succès une mémoire à accès aléatoire magnétorésistive à couple de transfert de spin (STT-MRAM) de densité 128 Mo avec une vitesse d'écriture de 14 ns pour une utilisation dans des applications de mémoire embarquée, tels que le cache dans l'IoT et l'IA. Il s'agit actuellement de la vitesse d'écriture la plus rapide au monde pour les applications de mémoire embarquée avec une densité supérieure à 100 Mo et ouvrira la voie à la production en série de STT-MRAM de grande capacité.

STT-MRAM est capable de fonctionner à grande vitesse et consomme très peu d'énergie, car il conserve les données même lorsque l'alimentation est coupée. En raison de ces caractéristiques, STT-MRAM gagne du terrain en tant que technologie de nouvelle génération pour des applications telles que la mémoire embarquée, mémoire principale et logique. Trois grandes usines de fabrication de semi-conducteurs ont annoncé que la production de masse à risque commencera en 2018.

La mémoire étant un élément essentiel des systèmes informatiques, appareils de poche et stockage, ses performances et sa fiabilité sont d'une grande importance pour les solutions énergétiques vertes.

La capacité actuelle de STT-MRAM est comprise entre 8Mb-40 Mb. Mais pour rendre STT-MRAM plus pratique, il est nécessaire d'augmenter la densité mémoire. L'équipe du Center for Innovative Integrated Electronic Systems (CIES) a augmenté la densité de mémoire de STT-MRAM en développant intensivement des STT-MRAM dans lesquelles des jonctions tunnel magnétiques (MTJ) sont intégrées au CMOS. Cela réduira considérablement la consommation d'énergie de la mémoire intégrée telle que le cache et la mémoire eFlash.

Les MTJ ont été miniaturisés grâce à une série de développements de processus. Pour réduire la taille de la mémoire nécessaire pour la STT-MRAM à plus haute densité, les MTJ ont été formés directement sur des trous de via, de petites ouvertures qui permettent une connexion conductrice entre les différentes couches d'un dispositif semi-conducteur. En utilisant la cellule mémoire de taille réduite, le groupe de recherche a conçu une STT-MRAM de 128 Mo de densité et fabriqué une puce.

Dans la puce fabriquée, les chercheurs ont mesuré une vitesse d'écriture de sous-tableau. Par conséquent, un fonctionnement à grande vitesse avec 14 ns a été démontré à une faible tension d'alimentation de 1,2 V. À ce jour, il s'agit de la vitesse d'écriture la plus rapide dans une puce STT-MRAM avec une densité supérieure à 100 Mo au monde.