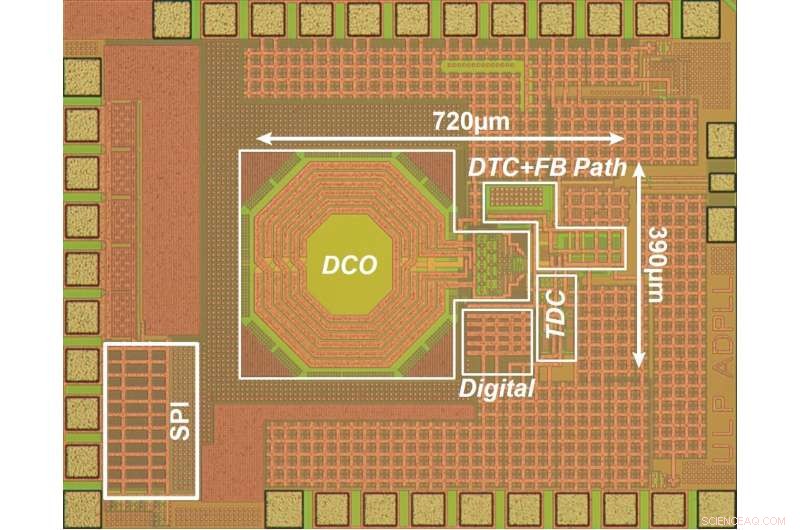

Le DPLL fractionné-N proposé occupe une superficie de 0,25 mm 2 en CMOS 65 nanomètres. Crédit :Kenichi Okada

Des scientifiques de l'Institut de technologie de Tokyo ont développé un synthétiseur de fréquence à boucle à verrouillage de phase (PLL) avancé qui peut réduire considérablement la consommation d'énergie. Cette PLL numérique pourrait être un élément de base attrayant pour Bluetooth Low Energy (BLE) et d'autres technologies sans fil afin de prendre en charge un large éventail d'applications Internet des objets (IoT).

En tant qu'élément clé des systèmes de communication sans fil, les synthétiseurs de fréquence doivent répondre à des exigences exigeantes. Bien que les synthétiseurs de fréquence PLL analogiques soient la norme depuis de nombreuses années, Les ingénieurs de l'industrie de l'IoT se tournent de plus en plus vers les PLL dites numériques (DPLL) pour obtenir un fonctionnement à très faible consommation d'énergie.

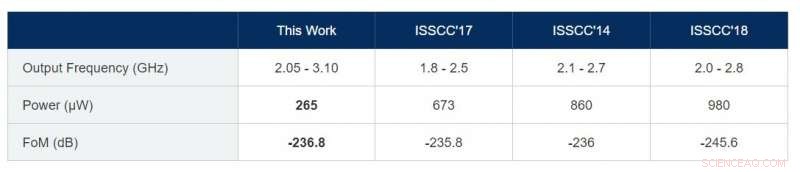

Kenichi Okada, professeur agrégé au Département de génie électrique et électronique de l'Institut de technologie de Tokyo et son groupe signalent maintenant une DPLL fractionnée N qui atteint une consommation d'énergie de seulement 265 microwatts (μW), un chiffre inférieur à la moitié de la plus faible consommation d'énergie réalisée à ce jour (980 μW). (Tableau 1)

Les chercheurs ont découvert que la consommation d'énergie globale pouvait être considérablement réduite en utilisant un système de contrôle de rétroaction automatique. "Ce chemin de retour à commutation automatique consomme une puissance de 68 W, ce qui conduit à une consommation électrique de 265 μW pour l'ensemble du DPLL, " dit Okada.

Le prometteur DPLL pourrait continuer à être utilisé comme composant pour les processeurs, mémoires et une vaste nouvelle gamme d'appareils IoT qui devraient être à la fois rentables et respectueux de l'environnement en fonctionnant à très faible consommation d'énergie. Okada note que les premières expériences montrent que le DPLL pourrait prolonger de quatre fois la durée de vie de la batterie.

Des scientifiques de l'Institut de technologie de Tokyo ont développé un synthétiseur de fréquence à boucle à verrouillage de phase (PLL) avancé qui peut réduire considérablement la consommation d'énergie. Cette PLL numérique pourrait être un élément de base attrayant pour Bluetooth Low Energy (BLE) et d'autres technologies sans fil afin de prendre en charge un large éventail d'applications Internet des objets (IoT). Crédit :Kenichi Okada

Ce document est partiellement basé sur les résultats obtenus à partir d'un projet commandé par la New Energy and Industrial Technology Development Organization (NEDO).

Ce travail est présenté dans le cadre de la session Frequency Synthesizers de la Conférence internationale des circuits à semi-conducteurs (ISSCC) 2019 le plus important forum annuel au monde sur les circuits à semi-conducteurs et les systèmes sur puce.