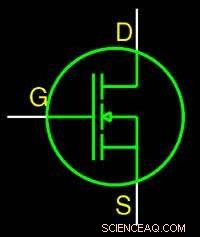

La contrainte mécanique de traction peut avoir un effet utile pour certains transistors, où la contrainte atomique résultante permet à ses paires électron-trou porteuses de courant une meilleure mobilité. Cependant, lorsque cette contrainte est appliquée à l'ensemble du dispositif, comme c'est une approche populaire via l'utilisation de ce qu'on appelle des couches d'arrêt de gravure de contact (CESL), la zone de dérive adjacente au canal étiré est comprimée et entraîne des performances réduites.

Une équipe de recherche en Chine a développé une nouvelle méthode CESL qui introduit une contrainte de traction à la fois dans le canal et dans la zone de dérive, améliorer les performances globales en offrant une faible résistance à la dérive, fréquence de coupure élevée et caractéristiques de claquage souhaitables. Leur travail est décrit dans un article paru cette semaine dans la revue Avances AIP .

L'équipe de chercheurs s'est intéressée à la méthode en raison des travaux effectués sur les techniques du silicium contraint. Au cours des recherches sur les transistors à effet de champ à semi-conducteurs méta-oxydes contraints (MOSFET), les chercheurs ont vu que la contrainte dans la région source/drain était inverse à la contrainte dans la région du canal. Sur la base de ces observations, ils ont commencé à étudier comment ils pourraient utiliser ce phénomène d'une manière qui pourrait améliorer les performances.

Cette nouvelle recherche s'est concentrée sur les dispositifs partiels de silicium sur isolant (PSOI) qui introduisent une contrainte de traction à la fois dans le canal et dans la région de dérive à l'aide des CESL. Les résultats de la simulation ont également montré que le dispositif PSOI offre de meilleures performances de fréquence et une meilleure capacité de conduite que les dispositifs sans contrainte.

"Le plus difficile pour nous a été de trouver un low cost, Méthode d'application de contraintes mécaniques compatible CMOS, " a déclaré Xiangzhan Wang, de l'Université des sciences et technologies électroniques de Chine. « Pendant le processus de fabrication, la plaquette se plie au fur et à mesure que le film de contrainte (Si3N4) grandit, ce qui crée un problème pour maintenir la plaquette dans l'équipement de traitement."

Les résultats de l'expérience, cependant, confiance accrue dans le fait que la nouvelle technique de déformation pourrait non seulement être appliquée à de petits appareils, mais aussi à des appareils assez volumineux pour améliorer les performances. Avec les résultats, même l'équipe de recherche a été surprise du niveau d'amélioration apporté à ses simulations.

« Dans notre simulation, le LDMOSFET de type n PSOI entièrement contraint en traction a montré une amélioration du courant d'entraînement de 20 à 30 % par rapport au LDMOSFET Si normal, " a déclaré Wang. " Mais lorsque nous avons utilisé cette méthode de contrainte avec un produit commercial Si LDMOS, le courant d'entraînement a doublé, ce qui a entraîné une augmentation du courant de plus de 100 %, ce qui était assez surprenant pour nous."

Bien que ce travail ait contribué à la compréhension des mécanismes du Si contraint, il y a encore plus à améliorer et à comprendre.

"Les prochaines directions de recherche de l'équipe sont d'optimiser le processus de fabrication de ces dispositifs afin d'obtenir une meilleure stabilité et d'essayer d'appliquer la même méthode à un dispositif non symétrique tel qu'un tunnel FET, " a dit Wang.