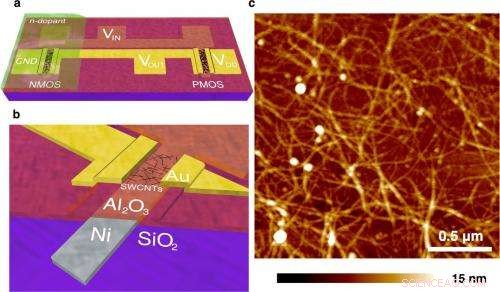

Illustrations de (a) l'inverseur CNT CMOS et (b) une coupe transversale d'un transistor CNT individuel, y compris une porte Ni de 25 nm d'épaisseur qui permet une consommation d'énergie ultra-faible. (c) Image de microscopie à force atomique de la morphologie du film CNT dans la région du canal du transistor. Crédit :Geier, et al. ©2013 Société chimique américaine

(Phys.org) — Les chercheurs ont démontré un nouveau dispositif logique à base de nanotubes de carbone (CNT) qui ne consomme que 0,1 nanowatt (nW) dans ses états statiques ON et OFF, représentant la valeur rapportée la plus basse de 3 ordres de grandeur pour les dispositifs logiques CMOS à base de CNT. L'appareil pourrait servir de bloc de construction pour de grandes surfaces, circuits logiques CNT à très faible consommation pouvant être utilisés pour réaliser une variété d'applications nanoélectroniques.

Les chercheurs, Michael L. Geier, et al., à l'Université Northwestern à Evanston, Illinois, et l'Université du Minnesota à Minneapolis, ont publié leur article sur la logique CNT subnanowatt dans un récent numéro de Nano lettres .

"Un circuit intégré moderne compte plus d'un milliard de transistors, " co-auteur Mark C. Hersam, Professeur de Science et Génie des Matériaux, Chimie, et médecine à l'Université Northwestern, Raconté Phys.org . "Par conséquent, la dissipation de puissance par transistor doit être très faible pour que l'ensemble du circuit ait une consommation électrique raisonnable. En réalité, il est généralement admis que la consommation d'énergie est le principal facteur limitant pour obtenir de nouvelles augmentations de la complexité (c'est-à-dire, nombre de transistors) dans les circuits intégrés."

Comme l'expliquent les chercheurs, l'un des plus grands avantages de l'architecture CMOS est qu'elle a une consommation d'énergie intrinsèquement faible. Cet avantage découle du fait que, contrairement aux autres architectures logiques, l'un des deux types de transistors (type p ou type n) est bloqué en régime permanent dans chaque porte logique des dispositifs CMOS.

Afin de tirer pleinement parti de ce potentiel de consommation électrique extrêmement faible, les transistors de type p et de type n doivent avoir des tensions de seuil réglées avec précision et bien séparées, qui sont les niveaux de tension qui déterminent si l'appareil est allumé ou éteint. Jusque là, cette question des tensions de seuil n'a pas été abordée, et les chercheurs ici l'ont identifié comme le défi clé limitant la réalisation d'électronique CMOS hautement intégrée à base de CNT.

Dans leur étude, les chercheurs ont utilisé une structure de grille métallique pour obtenir des tensions de seuil symétriques et clairement séparées pour les transistors CNT de type p et de type n, résultant en une consommation d'énergie ultra-faible. Dans les états statiques, dans lequel l'appareil est allumé ou éteint, la consommation électrique est inférieure à 0,1 nW. Au milieu de l'état de transfert, lorsque les transistors de type p et de type n sont simultanément à l'état passant, la tension atteint son pic à 10 nW.

En connectant plusieurs transistors CNT dans diverses configurations, les chercheurs ont démontré l'onduleur, Portes logiques NAND et NOR. À l'avenir, ces portes peuvent être intégrées dans des circuits complexes, où ils peuvent fournir une consommation d'énergie statique inférieure au nanowatt avec les autres avantages des CNT, telles que l'aptitude au traitement et la flexibilité de la solution.

"Nous travaillons maintenant à faire des circuits plus compliqués, où nous aurons sensiblement plus de transistors et de portes logiques en cascade, " a déclaré Hersam. " Nous avons également un intérêt à combiner des nanotubes de carbone avec d'autres matériaux nanoélectroniques émergents dans notre laboratoire (par exemple, bisulfure de molybdène [MoS

© 2013 Phys.org. Tous les droits sont réservés.