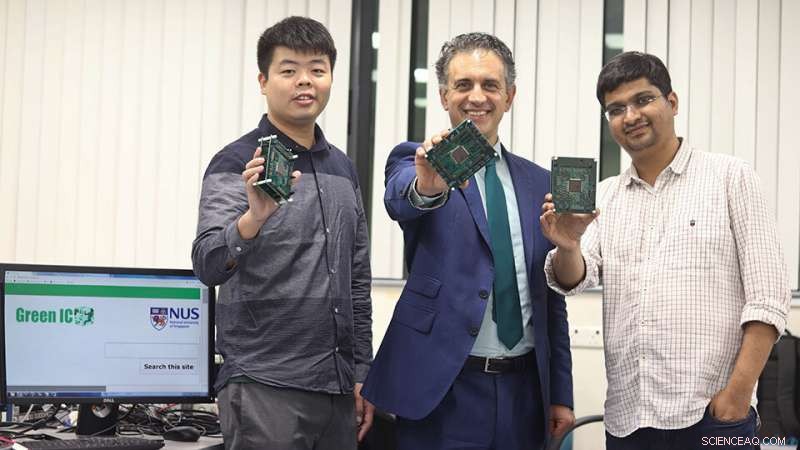

Assoc Prof Massimo Alioto (au centre) et les membres de son équipe Lin Longyang (à gauche) et Saurabh Jain (à droite) montrant les cartes de prototypage pour tester les puces de silicium afin de démontrer une puissance et des performances très flexibles, surpassant l'échelle de tension standard de l'industrie. Crédit :Université nationale de Singapour

Une équipe de chercheurs de NUS a inventé une nouvelle classe de techniques de reconfiguration qui étend de manière adaptative à la fois la consommation électrique minimale et les performances maximales des circuits numériques, bien au-delà de l'échelle de tension commune. Une telle adaptation étendue permet aux puces numériques de silicium de fonctionner à plus faible puissance lors d'une utilisation normale, et à un niveau de performance plus élevé si nécessaire.

Cela prolonge la durée de vie de la batterie en cas de disponibilité d'énergie incertaine dans les systèmes alimentés par des moissonneuses-batteuses (par exemple, une cellule solaire) ou des batteries rechargeables, tout en offrant des performances de pointe plus élevées pour effectuer des analyses de données sur puce lors de l'occurrence d'événements d'intérêt. Il s'agit d'un outil clé pour des applications telles que l'Internet des objets (IoT), intelligence artificielle (IA), wearables et dispositifs biomédicaux.

« Nos techniques de reconfiguration introduisent une adaptabilité sans précédent aux fluctuations de la disponibilité de l'alimentation et de la demande de performances. Par rapport à la technique de mise à l'échelle de la tension standard de l'industrie, des mesures sur plusieurs puces de test dans notre laboratoire ont montré qu'une telle adaptation prolonge de 1,5 fois la durée de vie de la batterie d'un appareil mobile ou portable, tout en doublant les performances de pointe. Nos techniques peuvent également être utilisées pour miniaturiser davantage la batterie par le même facteur, tout en conservant la même autonomie, " a expliqué le professeur agrégé Massimo Alioto de NUS Engineering. Il est le chef du groupe NUS Green IC qui est à l'origine de cette percée technologique.

Il ajouta, "Comme avantage supplémentaire, la polyvalence des performances de puissance de nos techniques de circuits permet aux sociétés de semi-conducteurs de simplifier leur portefeuille de puces et de réduire les coûts de conception, car la même conception numérique peut être réutilisée dans un large éventail d'applications et de marchés."

Les techniques proposées ont conduit à la démonstration d'accélérateurs et de processeurs (par exemple, Transformée de Fourier Rapide, processeurs ARM) avec une consommation d'énergie minimale signalée à ce jour. La recherche derrière les nouvelles techniques a été soutenue par les principales sociétés de semi-conducteurs (Intel, TSMC) ainsi que le ministère de l'Éducation de Singapour et la Fondation nationale de la recherche de Singapour.

Adaptation du chemin des données et de l'horloge :obtenir à la fois une faible consommation d'énergie minimale et des performances de pointe plus élevées

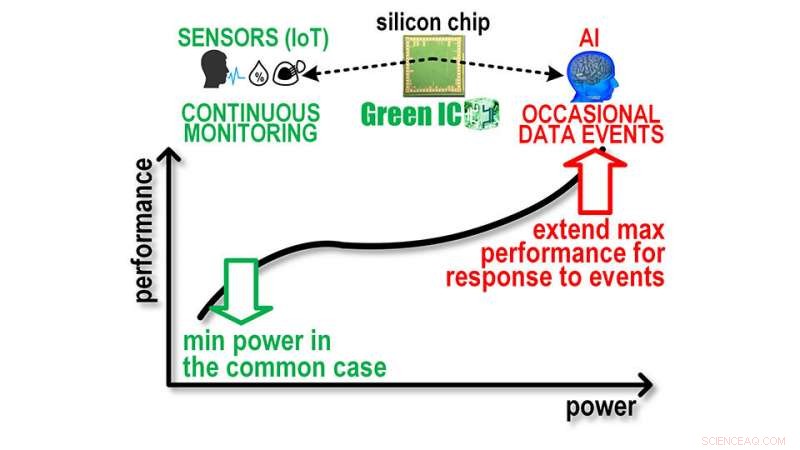

Mobile le plus avancé, Les applications IoT et AI nécessitent un compromis flexible et large entre la puissance moyenne (c'est-à-dire, vie de la batterie), et les performances maximales qui déterminent la réactivité du système (par exemple, lorsque l'écran est touché, ou effectuer des analyses de données lorsqu'un capteur produit des données d'intérêt).

Actuellement, la mise à l'échelle dynamique de la tension est l'étalon-or pour permettre une telle flexibilité. Le fonctionnement à des tensions d'environ 1 V conduit à des performances et une consommation d'énergie maximales, tandis que la réduction jusqu'à 0,4-0,5 V réduit la consommation d'énergie de quatre à cinq fois et ralentit la vitesse de fonctionnement de près de 10 fois. L'inconvénient de cette approche est que la mise à l'échelle de la tension s'applique généralement à une architecture numérique fixe, bien que l'architecture optimale pour la consommation d'énergie et les performances dépende de la tension adoptée.

Les circuits numériques adaptatifs démontrés par l'équipe NUS sont capables de prolonger la durée de vie de la batterie des puces de silicium intelligentes en réduisant la consommation d'énergie en utilisation normale, tout en augmentant les performances pour répondre rapidement aux événements de données occasionnels. Crédit :Université nationale de Singapour

L'invention NUS surpasse la mise à l'échelle de tension puisque sa reconfiguration de circuit permet une meilleure adéquation entre l'architecture et la tension adoptée, et par conséquent, une réduction supplémentaire de la consommation d'énergie et des améliorations des performances à différentes tensions peuvent être obtenues.

Le professeur agrégé Alioto a déclaré :"Notre invention permet la reconfiguration à la fois du "chemin de données" où le traitement réel est effectué, et le "chemin d'horloge" qui distribue le signal d'horloge pour orchestrer les différentes tâches de traitement. Dans les deux cas, leurs blocs de construction fondamentaux sont fusionnés ou divisés de manière flexible pour créer la structure de chemin de données et d'horloge qui améliore l'efficacité énergétique ou les performances à une tension donnée."

Par rapport à la mise à l'échelle de tension conventionnelle, l'approche proposée par le groupe NUS Green IC rend les circuits numériques plus polyvalents et adaptatifs, permettant une optimisation simultanée aux deux extrémités du spectre puissance-performance.

Livre technique et une chaîne d'outils complète accessibles au public

Partager les avantages de la nouvelle technique de l'équipe avec les groupes industriels et de recherche du monde entier, un livre technique a récemment été publié pour fournir le contexte et les détails de la mise en œuvre des puces de silicium des processeurs, accélérateurs et mémoires sur puce. Un flux de conception automatisé a également été créé et publié sur GitHub (Veuillez visiter www.green-ic.org/).

« Dans notre livre, nous avons introduit et démontré des méthodologies de conception en utilisant uniquement des outils de conception commerciaux, qui sont intégrés dans un flux de conception cohérent où la reconfiguration de l'horloge et du chemin de données est incorporée de manière plug-and-play. Nous sommes ravis de partager le code du logiciel de manière open source pour permettre l'adoption massive et rapide de nos nouvelles techniques dans le secteur commercial et dans la recherche académique, " a commenté le professeur agrégé Alioto.

Prochaines étapes

L'équipe de recherche NUS étudie actuellement le développement de nouvelles classes de systèmes de silicium intelligents qui permettent une adaptation ultra-large des performances de puissance dans les accélérateurs d'IA intégrés dans la détection de puces de silicium pour l'IoT. Cela conduira à des systèmes de nouvelle génération toujours disponibles, tout en étant capable de répondre rapidement à des événements externes avec des performances de calcul très importantes.

Dans leur travail, l'équipe s'efforce de permettre l'adaptation des performances énergétiques grâce à des techniques d'intégration et des méthodologies de conception dans les architectures système existantes. Cela permet d'obtenir des avantages en termes de puissance et de performances sans perturber l'écosystème de conception, permettant ainsi une adoption rapide et massive des systèmes intelligents de nouvelle génération.