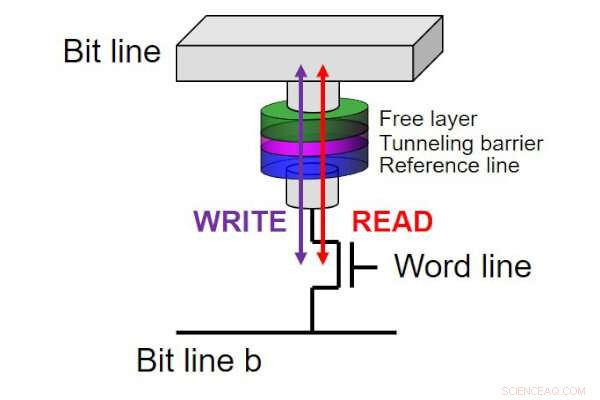

Schéma de la cellule STT-MRAM (Two Terminal Device). Crédit :CIES, Université du Tohoku

Des chercheurs de l'Université de Tohoku ont annoncé la démonstration d'une cellule mémoire à accès aléatoire magnétorésistive à couple de rotation-orbite (SOT) à grande vitesse compatible avec la technologie CMOS Si 300 mm.

La demande de circuits intégrés (CI) basse consommation et hautes performances a augmenté à mesure que les dispositifs d'intelligence artificielle (IA) et d'Internet des objets (IoT) sont de plus en plus adoptés. Avec les circuits intégrés actuels, Les mémoires purement CMOS telles que la mémoire Flash embarquée (eFlash) et la mémoire statique à accès aléatoire (SRAM) sont responsables d'une forte proportion de la consommation d'énergie. Afin de réduire la consommation d'énergie tout en gardant des performances élevées, Les mémoires magnétorésistives à accès aléatoire (MRAM) ont été intensivement développées. Les MRAM à couple de transfert de spin (STT-MRAM) sont les MRAM les plus développées. Les principales sociétés de semi-conducteurs ont maintenant annoncé qu'elles étaient prêtes pour la production en série de STT-MRAM pour le remplacement de l'eFlash.

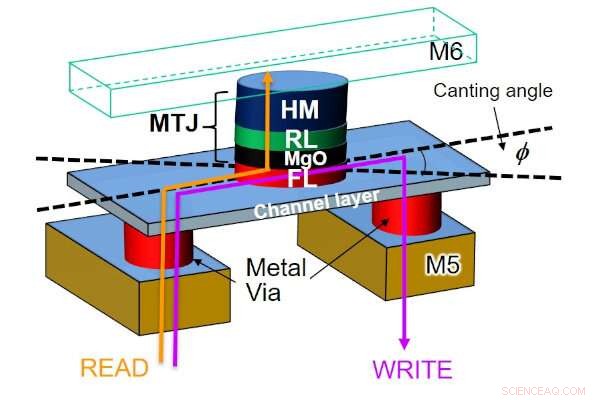

Les chercheurs visent à remplacer la SRAM par la MRAM. Pour le remplacement de la SRAM, La MRAM doit atteindre une vitesse de fonctionnement supérieure à 500 MHz. Pour répondre à la demande, une MRAM alternative, une MRAM à couple de rotation-orbite (SOT-MRAM) a été proposée, qui présente plusieurs avantages pour un fonctionnement à grande vitesse. En raison de ces avantages, SOT-MRAM a également été développé; cependant, la plupart des études de laboratoire se concentrent sur les principes fondamentaux des dispositifs SOT. Pour réaliser le remplacement de SRAM par SOT-MRAM, il est nécessaire de démontrer les hautes performances de la cellule mémoire SOT-MRAM sur un substrat CMOS de 300 mm. En outre, il est nécessaire de développer le processus d'intégration pour SOT-MRAM, par exemple., tolérance thermique contre le recuit à 400 °C, qui est une exigence du processus de fin de ligne CMOS standard.

Un schéma de la cellule SOT-MRAM (Three Terminal Device) Crédit :CIES, Université du Tohoku

Une vue schématique de la cellule SOT-MRAM inclinée. Crédit :CIES, Université du Tohoku

L'équipe de recherche dirigée par les professeurs Tetsuo Endoh et Hideo Ohno, l'actuel président de l'Université de Tohoku, a développé un processus d'intégration pour les dispositifs SOT compatibles avec la technologie CMOS 55 nm et fabriqué des dispositifs SOT sur des substrats CMOS 300 mm. Le dispositif SOT nouvellement développé a atteint simultanément une commutation à grande vitesse jusqu'à 0,35 ns et un facteur de stabilité thermique suffisamment élevé (E/k

Ces réalisations ont résolu les problèmes pour rendre SOT-MRAM pratique pour les applications commerciales et offrir ainsi un moyen de remplacer SRAM par SOT-MRAM, qui contribuera à la réalisation d'une électronique performante à faible consommation électrique.

Les résultats seront présentés à l'IEEE International Electron Devices Meeting 2019 à San Francisco, 7-11 décembre, 2019.