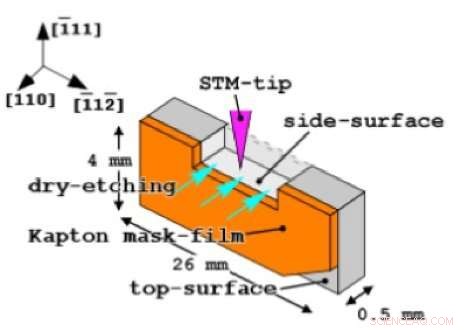

Figure 1. Un schéma d'un échantillon de Si(110) avec un masque de film Kapton :gravure sèche de la surface supérieure (110) et pointe STM approchant de la surface latérale (-111). Crédit :Université d'Osaka

Une collaboration de recherche entre l'Université d'Osaka et l'Institut des sciences et technologies de Nara a utilisé pour la première fois la microscopie à effet tunnel (STM) pour créer des images de surfaces latérales atomiquement plates de cristaux de silicium 3-D. Ce travail aide les fabricants de semi-conducteurs à continuer d'innover tout en produisant des plus rapide, et des puces informatiques plus économes en énergie pour les ordinateurs et les smartphones.

Nos ordinateurs et nos smartphones sont chacun chargés de millions de minuscules transistors. La vitesse de traitement de ces dispositifs a considérablement augmenté au fil du temps, à mesure que le nombre de transistors pouvant tenir sur une seule puce informatique continue d'augmenter. Basé sur la loi de Moore, le nombre de transistors par puce doublera environ tous les 2 ans, et dans ce domaine, il semble tenir le coup. Pour suivre ce rythme d'innovation rapide, les fabricants d'ordinateurs sont continuellement à la recherche de nouvelles méthodes pour rendre chaque transistor toujours plus petit.

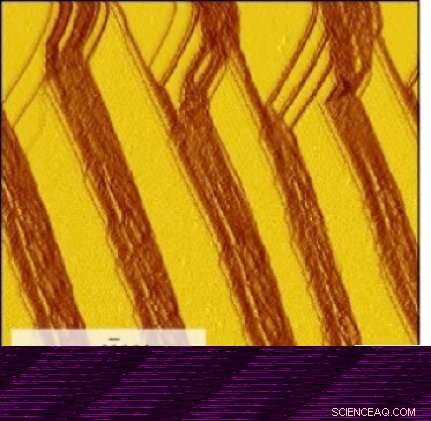

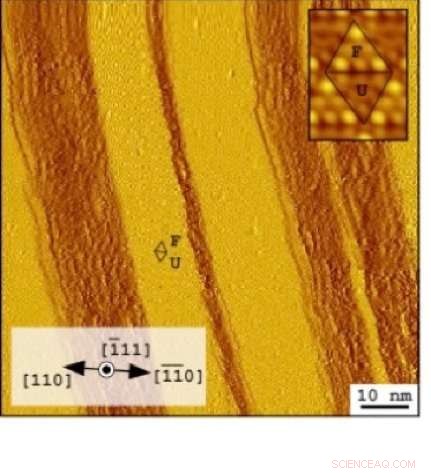

Figure 3. Images STM dérivées spatiales avec 200x200 nm^2 à Vs =+1,5 V. Les terrasses plates deviennent plus lumineuses et les bords plus sombres. La direction du bas va de gauche ((110) surface supérieure) à droite ((-1-10) surface arrière). Crédit :Université d'Osaka

Les microprocesseurs actuels sont fabriqués en ajoutant des motifs de circuits à des plaquettes de silicium plates. Une nouvelle façon d'entasser plus de transistors dans le même espace consiste à fabriquer des structures 3-D. Les transistors à effet de champ (FET) de type à ailettes sont nommés ainsi car ils ont des structures de silicium en forme d'ailettes qui s'étendent dans l'air, hors de la surface de la puce. Cependant, cette nouvelle méthode nécessite un cristal de silicium avec un dessus et des surfaces latérales parfaitement plats, au lieu de juste la surface supérieure, comme avec les appareils actuels. La conception de la prochaine génération de puces nécessitera de nouvelles connaissances sur les structures atomiques des surfaces latérales.

Figure 3. Images STM dérivées spatiales avec 200x200 nm^2 à Vs =+1,5 V. Les terrasses plates deviennent plus lumineuses et les bords plus sombres. La direction du bas va de gauche ((110) surface supérieure) à droite ((-1-10) surface arrière). Crédit :Université d'Osaka

Maintenant, Des chercheurs de l'Université d'Osaka et de l'Institut des sciences et technologies de Nara rapportent qu'ils ont utilisé pour la première fois la STM pour imager la surface latérale d'un cristal de silicium. STM est une technique puissante qui permet de voir les emplacements des atomes de silicium individuels. En passant une pointe acérée très près de l'échantillon, les électrons peuvent sauter à travers l'espace et créer un courant électrique. Le microscope a surveillé ce courant, et déterminé l'emplacement des atomes dans l'échantillon.

"Notre étude est une première étape importante vers l'évaluation à résolution atomique des transistors conçus pour avoir des formes 3-D, ", explique Azusa Hattori, co-auteur de l'étude.

Pour rendre les surfaces latérales aussi lisses que possible, les chercheurs ont d'abord traité les cristaux avec un processus appelé gravure ionique réactive. Le coauteur Hidekazu Tanaka dit :"Notre capacité à regarder directement les surfaces latérales à l'aide de STM prouve que nous pouvons créer des structures 3D artificielles avec un ordre de surface atomique presque parfait."