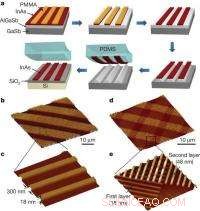

La fabrication d'un dispositif à base d'oxyde d'indium (InAs) commence par a) la croissance épitaxiale et la gravure d'InAs en réseaux de nanorubans qui sont estampés sur un substrat de silicium/silice (Si/SiO2) ; b) et c) des réseaux de nanorubans d'InAs sur Si/SiO2 ; d) et e) Superstructures de nanoruban d'InAs sur Si/SiO2. Crédit :avec l'aimable autorisation d'Ali Javey, UC Berkeley

Il y a de bonnes nouvelles dans la recherche de la prochaine génération de semi-conducteurs. Des chercheurs du Lawrence Berkeley National Laboratory du Département de l'énergie des États-Unis et de l'Université de Californie à Berkeley, ont réussi à intégrer des couches ultra-minces d'arséniure d'indium semi-conducteur sur un substrat de silicium pour créer un transistor nanométrique doté d'excellentes propriétés électroniques. Un membre de la famille III-V de semi-conducteurs, l'arséniure d'indium offre plusieurs avantages comme alternative au silicium, notamment une mobilité et une vitesse supérieures des électrons, ce qui en fait un candidat de choix pour la future basse consommation, appareils électroniques à grande vitesse.

"Nous avons montré une voie simple pour l'intégration hétérogène de couches d'arséniure d'indium jusqu'à une épaisseur de 10 nanomètres sur des substrats de silicium, " dit Ali Javey, chercheur à la faculté des sciences des matériaux du Berkeley Lab et professeur de génie électrique et d'informatique à l'UC Berkeley, qui a mené cette recherche.

« Les dispositifs que nous avons fabriqués par la suite se sont avérés fonctionner près des limites de performances prévues des dispositifs III-V avec un courant de fuite minimal. Nos dispositifs ont également présenté des performances supérieures en termes de densité de courant et de transconductance par rapport aux transistors au silicium de dimensions similaires. »

Pour toutes ses merveilleuses propriétés électroniques, le silicium a des limites qui ont incité une recherche intense de semi-conducteurs alternatifs à utiliser dans les futurs appareils. Javey et son groupe de recherche se sont concentrés sur les semi-conducteurs composés III-V, qui présentent de superbes propriétés de transport d'électrons. Le défi a été de trouver un moyen de brancher ces semi-conducteurs composés dans le système bien établi, technologie de traitement à faible coût utilisée pour produire les dispositifs à base de silicium d'aujourd'hui. Compte tenu de la grande disparité de réseau entre le silicium et les semi-conducteurs composés III-V, la croissance hétéro-épitaxiale directe de III-V sur des substrats de silicium est difficile et complexe, et entraîne souvent un volume élevé de défauts.

"Nous avons démontré ce que nous appelons un" XOI, ' ou plate-forme technologique composée de semi-conducteurs sur isolant, qui est parallèle au "SOI" d'aujourd'hui, ' ou plate-forme silicium sur isolant, " dit Javey. " En utilisant une méthode de transfert épitaxiale, nous avons transféré des couches ultrafines d'arséniure d'indium monocristallin sur des substrats de silicium/silice, puis ont fabriqué des appareils en utilisant des techniques de traitement conventionnelles afin de caractériser le matériau XOI et les propriétés de l'appareil."

Les résultats de cette recherche ont été publiés dans la revue La nature, dans un article intitulé, "Semiconducteur composé ultra-mince sur couches isolantes pour transistors nanométriques haute performance." Les co-auteurs du rapport avec Javey étaient Hyunhyub Ko, Kuniharu Takei, Rehan Kapadia, Steven Chuang, Hui Fang, Paul Leu, Kartik Ganapathi, Hélène Plis, Ha Sul Kim, Szu Ying Chen, Morten Madsen, Alexandra Ford, Yu-Lun Chueh, Sanjay Krishna et Sayeef Salahuddin.

Pour faire leurs plateformes XOI, Javey et ses collaborateurs ont développé des films minces monocristallins d'arséniure d'indium (10 à 100 nanomètres d'épaisseur) sur un substrat source préliminaire, puis ont modelé les films par lithographie en réseaux ordonnés de nanorubans. Après avoir été retiré du substrat source par une gravure humide sélective d'une couche sacrificielle sous-jacente, les réseaux de nanorubans ont été transférés sur le substrat de silicium/silice via un processus d'estampage.

Javey a attribué les excellentes performances électroniques des transistors XOI aux petites dimensions de la couche "X" active et au rôle critique joué par le confinement quantique, qui a servi à régler la structure de bande et les propriétés de transport du matériau. Bien que lui et son groupe n'aient utilisé que l'arséniure d'indium comme semi-conducteur composé, la technologie devrait également s'adapter facilement à d'autres semi-conducteurs composés III/V.

« Des recherches futures sur l'évolutivité de notre processus pour le traitement des plaquettes de 8 pouces et de 12 pouces sont nécessaires, " a déclaré Javey.

"Pour aller de l'avant, nous pensons que les substrats XOI peuvent être obtenus grâce à un processus de collage de plaquettes, mais notre technique devrait permettre de fabriquer à la fois des transistors de type p et n sur la même puce pour une électronique complémentaire basée sur des semi-conducteurs III-V optimaux.

"En outre, ce concept permet d'intégrer directement des photodiodes hautes performances, laser, et des diodes électroluminescentes sur des substrats de silicium conventionnels. Unique, cette technique pourrait nous permettre d'étudier les propriétés matérielles de base des semi-conducteurs inorganiques lorsque l'épaisseur est réduite à seulement quelques couches atomiques."