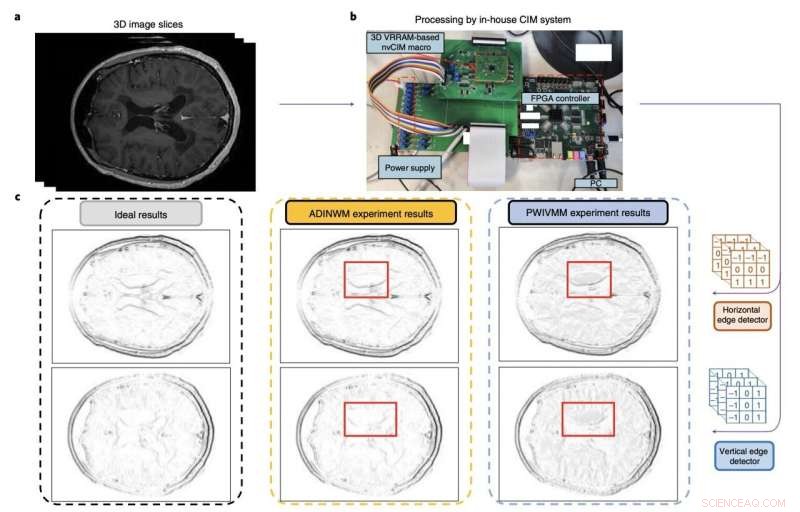

Figure résumant l'évaluation et les performances de la macro de calcul en mémoire des chercheurs. Crédit :Huo et al (Nature Electronics , 2022).

Les architectures d'apprentissage automatique basées sur les réseaux de neurones convolutifs (CNN) se sont avérées très utiles pour un large éventail d'applications, allant de la vision par ordinateur à l'analyse d'images et au traitement ou à la génération du langage humain. Cependant, pour s'attaquer à des tâches plus avancées, ces architectures deviennent de plus en plus complexes et exigeantes en termes de calcul.

Ces dernières années, de nombreux ingénieurs électroniciens du monde entier ont donc essayé de développer des dispositifs capables de prendre en charge le stockage et la charge de calcul d'architectures complexes basées sur CNN. Cela inclut des dispositifs de mémoire plus denses qui peuvent prendre en charge de grandes quantités de poids (c'est-à-dire les paramètres entraînables et non entraînables pris en compte par les différentes couches de CNN).

Des chercheurs de l'Académie chinoise des sciences, de l'Institut de technologie de Pékin et d'autres universités chinoises ont récemment développé un nouveau système de calcul en mémoire qui pourrait aider à exécuter plus efficacement des modèles basés sur CNN plus complexes. Leur composant mémoire, présenté dans un article publié dans Nature Electronics , est basé sur des macros de calcul en mémoire non volatiles constituées de tableaux de memristors 3D.

"La mise à l'échelle de tels systèmes sur des matrices 3D pourrait fournir un parallélisme, une capacité et une densité plus élevés pour les opérations de multiplication de matrice vectorielle nécessaires", ont écrit Qiang Huo et ses collègues dans leur article. "Cependant, la mise à l'échelle en trois dimensions est difficile en raison de problèmes de fabrication et de variabilité des appareils. Nous rapportons une macro de calcul en mémoire non volatile de deux kilobits basée sur une mémoire à accès aléatoire résistive verticale tridimensionnelle fabriquée à l'aide d'un 55 nm procédé complémentaire métal-oxyde-semi-conducteur."

Les mémoires résistives à accès aléatoire, ou RRAM, sont des dispositifs de stockage non volatils (c'est-à-dire qui conservent les données même après des coupures d'alimentation) basés sur des memristors. Les memristors sont des composants électroniques qui peuvent limiter ou réguler le flux de courant électrique dans les circuits, tout en enregistrant la quantité de charge qui les traversait auparavant.

Les RRAM fonctionnent essentiellement en faisant varier la résistance à travers un memristor. Alors que des études antérieures ont démontré le grand potentiel de ces dispositifs de mémoire, les versions conventionnelles de ces dispositifs sont séparées des moteurs informatiques, ce qui limite leurs applications possibles.

Les dispositifs RRAM de calcul en mémoire ont été conçus pour surmonter cette limitation, en intégrant les calculs à l'intérieur de la mémoire. Cela peut réduire considérablement le transfert de données entre les mémoires et les processeurs, améliorant ainsi l'efficacité énergétique globale du système.

Le dispositif de calcul en mémoire créé par Huo et ses collègues est une RRAM 3D avec des couches et des circuits périphériques empilés verticalement. Les circuits de l'appareil ont été fabriqués à l'aide de la technologie CMOS 55 nm, la technologie qui sous-tend la plupart des circuits intégrés sur le marché aujourd'hui.

Les chercheurs ont évalué leur appareil en l'utilisant pour effectuer des opérations complexes et pour exécuter un modèle de détection des bords dans les IRM cérébrales. L'équipe a formé ses modèles à l'aide de deux ensembles de données IRM existants pour former des outils de reconnaissance d'images, connus sous le nom d'ensembles de données MNIST et CIFAR-10.

"Notre macro peut effectuer des opérations de multiplication de matrice vectorielle 3D avec une efficacité énergétique de 8,32 téra-opérations par seconde par watt lorsque les données d'entrée, de poids et de sortie sont respectivement de 8,9 et 22 bits, et que la densité de bits est de 58,2 bit µm. –2 ", ont écrit les chercheurs dans leur article. "Nous montrons que la macro offre une détection plus précise des contours de l'IRM cérébrale et une meilleure précision d'inférence sur l'ensemble de données CIFAR-10 que les méthodes conventionnelles."

Lors des premiers tests, le système RRAM vertical de calcul en mémoire créé par Huo et ses collègues a obtenu des résultats remarquables, surpassant les approches RRAM conventionnelles. À l'avenir, il pourrait donc s'avérer très utile pour exécuter des modèles complexes basés sur CNN de manière plus économe en énergie, tout en permettant de meilleures précisions et performances.

© 2022 Réseau Science X Une macro nvCIM de quatre mégabits pour les appareils d'intelligence artificielle de périphérie