L'équipe NUS Green IC :Dr Orazio Aiello (à gauche) et professeur agrégé Massimo Alioto (à droite). Crédit :Université nationale de Singapour

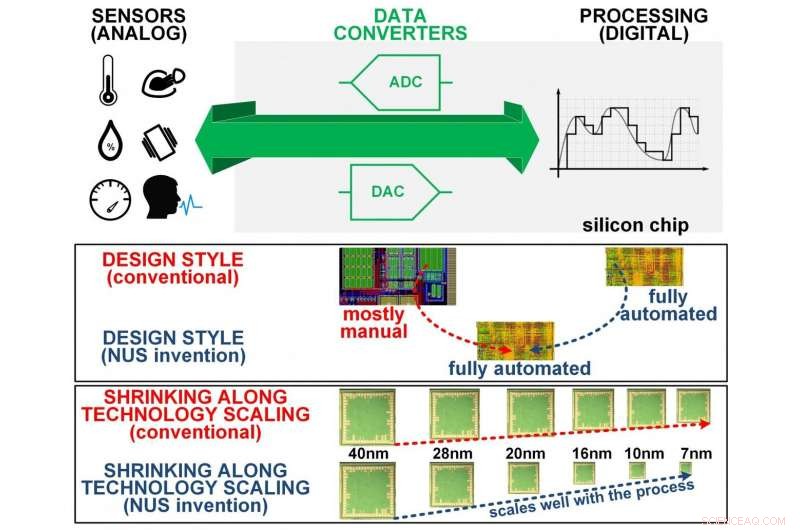

Le groupe de recherche Green IC du département de génie électrique et informatique de la faculté d'ingénierie de l'Université nationale de Singapour (NUS) a inventé une nouvelle classe de convertisseurs numérique-analogique (DAC) et analogique-numérique (ADC) qui peuvent être entièrement conçu avec une méthodologie de conception numérique entièrement automatisée, grâce à son architecture entièrement numérique (Fig. 1).

Par rapport aux architectures et méthodologies analogiques traditionnelles, le délai de conception de ces nouvelles interfaces de capteurs est réduit de quelques mois à quelques heures. La réduction drastique de l'effort de conception est très bénéfique dans les systèmes au silicium sensibles aux coûts, tels que les capteurs pour l'Internet des objets (IoT). La nouvelle architecture de convertisseur de données a également une très faible complexité, réduire d'au moins 30 fois la surface de silicium et donc le coût de fabrication, par rapport aux conceptions conventionnelles.

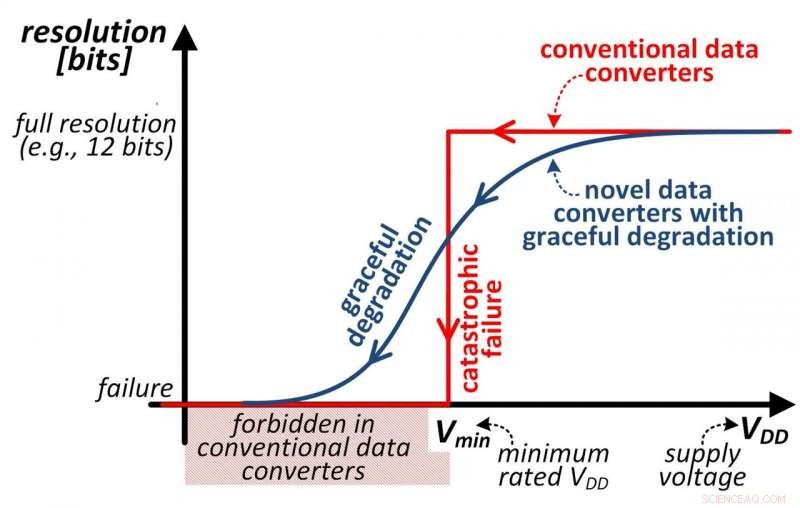

Ces nouveaux convertisseurs de données présentent également la capacité sans précédent de dégrader gracieusement la fidélité du signal lorsque sa tension d'alimentation ou sa fréquence d'horloge subissent de grandes fluctuations (Fig. 2). De telles fluctuations sont courantes dans les capteurs IoT à récupération d'énergie, étant que la puissance récupérée de l'environnement environnant (par exemple, cellule solaire) est très erratique. À son tour, cela permet une surveillance ininterrompue du signal du capteur même dans des conditions de puissance récoltée défavorables, et sans régulation de tension. Au lieu, les convertisseurs de données traditionnels souffrent d'une dégradation catastrophique de la résolution lorsque la tension d'alimentation est inférieure à sa valeur nominale minimale Vmin (ou que la fréquence dépasse sa valeur nominale maximale) comme dans la Fig. 2, nécessitant donc des circuits gourmands en énergie pour la régulation de la tension et de la fréquence.

La recherche a été menée en collaboration avec le professeur agrégé Paolo Crovetti du Politecnico di Torino en Italie, et est soutenu par le ministère de l'Éducation de Singapour et la Commission européenne.

Interfaces de capteurs plus petites, plus simple et plus rapide à concevoir

"Notre recherche transforme la conception traditionnellement analogique et principalement manuelle des convertisseurs de données en une conception numérique entièrement automatisée, réduire la surface du silicium d'un ordre de grandeur et le temps de conception de deux ordres de grandeur, permettre aux entreprises de semi-conducteurs d'être compétitives en termes de coûts tout en atteignant les marchés plus rapidement, " a déclaré le chef d'équipe, le professeur agrégé Massimo Alioto, qui est du département de génie électrique et informatique de la faculté de génie NUS.

Une défaillance catastrophique est remplacée par une dégradation progressive de la résolution dans la nouvelle classe de convertisseurs de données conventionnels inventée par l'équipe NUS. Cela permet de simplifier considérablement la conception du système, supprimant le besoin d'une régulation précise de la tension. Crédit :Université nationale de Singapour

Il ajouta, "Être numérique, nos interfaces de capteurs sont facilement portées à travers les technologies de fabrication et les applications, et peuvent être immergés dans des circuits numériques pour éviter l'effort traditionnel requis par leur intégration sur une même puce de silicium." (Fig. 1).

L'équipe NUS a démontré le concept à travers plusieurs puces de silicium mettant en œuvre à la fois des DAC et des ADC avec une surface extrêmement faible. Par exemple, un DAC 12 bits fabriqué en technologie CMOS standard 40 nm a été démontré avec une surface égale au diamètre d'un cheveu humain. Sa capacité inhérente à la mise à l'échelle de la technologie le fait rétrécir d'environ 32 fois lorsqu'il est mis en œuvre dans la technologie actuellement la plus fine (7 nm).

À la fois, il a été démontré que l'invention NUS permet des convertisseurs de données avec des résolutions élevées (jusqu'à 16 bits), tout en atteignant la simplicité de conception et la compacité.

Membre de l'équipe Dr. Orazio Aiello, qui est chercheur invité au Département, mentionné, « Notre équipe a introduit un nouveau paradigme de conception qui nous rapproche de la vision ultime du bon marché, des appareils IoT ultra-compacts et évolutifs sur le plan technologique."

Une robustesse sans précédent apporte des avantages supplémentaires au niveau du système

L'innovation NUS simplifie davantage la conception du système intégré, en s'appuyant sur une capacité sans précédent à résister à des fluctuations de tension et de fréquence très importantes, assouplissant ainsi les exigences de précision dans la génération de tension et de fréquence.

Une défaillance catastrophique est remplacée par une dégradation progressive de la résolution dans la nouvelle classe de convertisseurs de données conventionnels inventés par les chercheurs du NUS. Crédit :Université nationale de Singapour

En effet, les convertisseurs de données conventionnels fonctionnant à une tension d'alimentation inférieure à sa valeur nominale minimale (ou à une fréquence d'horloge excessive) subissent une défaillance catastrophique, et ne parvient donc pas à remplir sa fonction prévue (Fig. 2). Au contraire, les convertisseurs de données innovants inventés par l'équipe NUS présentent une dégradation progressive de la résolution et de la fidélité du signal lorsque la tension d'alimentation ou la fréquence d'horloge dépasse sa plage autorisée. Par exemple, un DAC conçu pour 1 V s'est avéré fonctionner correctement à la moitié de cette tension, tout en dégradant sa résolution de seulement 1 bit lorsque la tension d'alimentation est réduite de 0,3V substantielle.

Assoc Prof Alioto a dit, "La capacité d'avoir une dégradation de la résolution gracieuse sous tension et fréquence excessive supprime le besoin de solutions de circuits complexes qui régulent avec précision la tension d'alimentation et la fréquence d'horloge utilisées par les convertisseurs de données. En d'autres termes, nos convertisseurs de données sont plus simples à concevoir, et aussi simplifier le système dans lequel ils sont employés."

Prochaines étapes

L'équipe travaille actuellement sur un nouveau paradigme qui transforme les sous-systèmes de silicium traditionnellement analogiques et à conception intensive en conceptions numériques standard basées sur des cellules qui sont prises en charge par des flux de conception entièrement automatisés, repousser les limites de la conception classique assistée par voie numérique. Cette étude de recherche implique plusieurs sous-systèmes fondamentaux tels que les amplificateurs, oscillateurs, références de tension et de courant, et plein d'autres.

L'équipe de recherche vise à transformer la façon dont les systèmes intégrés sont conçus, permettant ultra-rapide, conception ultra-compacte et technologiquement portable de systèmes entiers.