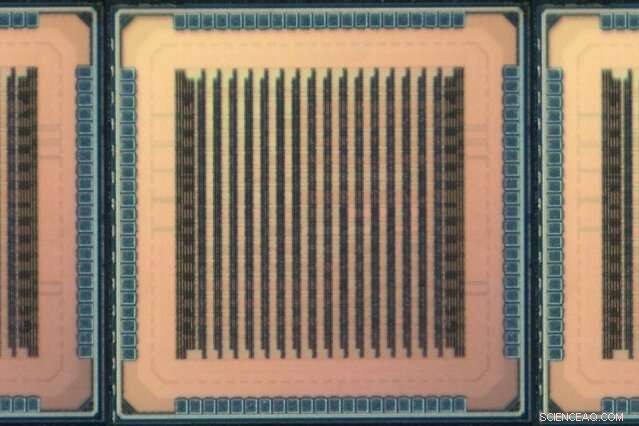

Des chercheurs du MIT ont mis au point une nouvelle puce capable de calculer des schémas de cryptage complexes à l'épreuve des quantums suffisamment efficacement pour protéger les appareils « Internet des objets » (IoT) à faible consommation d'énergie. Crédit :Massachusetts Institute of Technology

Des chercheurs du MIT ont mis au point un nouveau circuit de cryptographie qui peut être utilisé pour protéger les appareils « Internet des objets » (IoT) à faible consommation dans l'ère à venir de l'informatique quantique.

Les ordinateurs quantiques peuvent en principe exécuter des calculs qui sont aujourd'hui pratiquement impossibles pour les ordinateurs classiques. La mise en ligne et la commercialisation des ordinateurs quantiques pourraient un jour permettre des avancées dans la recherche médicale, découverte de médicament, et d'autres applications. Mais il y a un hic :si les pirates ont également accès aux ordinateurs quantiques, ils pourraient potentiellement percer les puissants schémas de cryptage qui protègent actuellement les données échangées entre les appareils.

Le schéma de cryptage résistant quantique le plus prometteur d'aujourd'hui est appelé "cryptographie basée sur réseau, " qui cache des informations dans des structures mathématiques extrêmement compliquées. A ce jour, aucun algorithme quantique connu ne peut briser ses défenses. Mais ces schémas sont beaucoup trop intenses en calcul pour les appareils IoT, qui ne peut économiser assez d'énergie que pour un simple traitement de données.

Dans un article présenté à la récente Conférence internationale sur les circuits à semi-conducteurs, Les chercheurs du MIT décrivent une nouvelle architecture de circuit et des astuces d'optimisation statistique qui peuvent être utilisées pour calculer efficacement la cryptographie basée sur le réseau. Les puces de 2 millimètres carrés que l'équipe a développées sont suffisamment efficaces pour être intégrées dans n'importe quel appareil IoT actuel.

L'architecture est personnalisable pour s'adapter aux multiples schémas à base de treillis actuellement à l'étude en vue du jour où les ordinateurs quantiques seront mis en ligne. "Cela pourrait être dans quelques décennies, mais déterminer si ces techniques sont vraiment sûres prend du temps, " dit le premier auteur Utsav Banerjee, un étudiant diplômé en génie électrique et en informatique. « Cela peut sembler tôt, mais plus tôt, c'est toujours mieux."

De plus, disent les chercheurs, le circuit est le premier du genre à répondre aux normes de cryptographie à base de réseau définies par le National Institute of Standards and Technology (NIST), une agence du Département du Commerce des États-Unis qui trouve et rédige des réglementations pour les schémas de cryptage d'aujourd'hui.

Rejoindre Banerjee sur le papier sont Anantha Chandrakasan, doyen de la School of Engineering du MIT et professeur Vannevar Bush de génie électrique et d'informatique, et Abhishek Pathak de l'Institut indien de technologie.

Échantillonnage efficace

Au milieu des années 90, Le professeur du MIT Peter Shor a développé un algorithme quantique qui peut essentiellement percer tous les schémas de cryptographie modernes. Depuis, Le NIST a essayé de trouver les schémas de cryptage post-quantique les plus sûrs. Cela se produit par phases ; chaque phase établit une liste des schémas les plus sûrs et les plus pratiques. Il y a deux semaines, l'agence est entrée dans sa deuxième phase de cryptographie postquantique, avec des schémas à base de treillis constituant la moitié de sa liste.

Dans la nouvelle étude, les chercheurs ont d'abord mis en œuvre sur des microprocesseurs commerciaux plusieurs schémas de cryptographie basés sur le réseau NIST de la première phase de l'agence. Cela a révélé deux goulots d'étranglement pour l'efficacité et les performances :la génération de nombres aléatoires et le stockage de données.

La génération de nombres aléatoires est la partie la plus importante de tous les schémas de cryptographie, car ces nombres sont utilisés pour générer des clés de chiffrement sécurisées qui ne peuvent pas être prédites. Cela est calculé grâce à un processus en deux parties appelé « échantillonnage ».

L'échantillonnage génère d'abord des nombres pseudo-aléatoires à partir d'un nombre connu, ensemble fini de valeurs qui ont une probabilité égale d'être sélectionnées. Puis, une étape de "post-traitement" convertit ces nombres pseudo-aléatoires en une distribution de probabilité différente avec un écart type spécifié - une limite pour combien les valeurs peuvent varier les unes des autres - qui randomise davantage les nombres. Essentiellement, les nombres aléatoires doivent satisfaire à des paramètres statistiques soigneusement choisis. Ce problème mathématique difficile consomme environ 80 pour cent de toute l'énergie de calcul nécessaire à la cryptographie basée sur les réseaux.

Après avoir analysé toutes les méthodes disponibles pour l'échantillonnage, les chercheurs ont découvert qu'une méthode, appelé SHA-3, peut générer de nombreux nombres pseudo-aléatoires deux ou trois fois plus efficacement que tous les autres. Ils ont modifié SHA-3 pour gérer l'échantillonnage cryptographique basé sur le réseau. En plus de cela, ils ont appliqué quelques astuces mathématiques pour faire un échantillonnage pseudo-aléatoire, et la conversion du post-traitement vers de nouvelles distributions, plus rapide et plus efficace.

Ils exécutent cette technique à l'aide d'un matériel personnalisé écoénergétique qui n'occupe que 9 % de la surface de leur puce. À la fin, cela rend le processus d'échantillonnage de deux ordres de grandeur plus efficace que les méthodes traditionnelles.

Diviser les données

Côté matériel, les chercheurs ont fait des innovations dans le flux de données. La cryptographie à base de treillis traite les données dans des vecteurs, qui sont des tableaux de quelques centaines ou milliers de nombres. Le stockage et le déplacement de ces données nécessitent des composants de mémoire physique qui occupent environ 80 % de la surface matérielle d'un circuit.

Traditionnellement, les données sont stockées sur un seul dispositif de mémoire vive (RAM) à deux ou quatre ports. Les périphériques multiports permettent le débit de données élevé requis pour les schémas de cryptage, mais ils prennent beaucoup de place.

Pour leur conception de circuit, les chercheurs ont modifié une technique appelée « transformation théorique des nombres » (NTT), qui fonctionne de manière similaire à la technique mathématique de la transformée de Fourier qui décompose un signal en les multiples fréquences qui le composent. Le NTT modifié divise les données vectorielles et alloue des portions sur quatre périphériques RAM à port unique. Chaque vecteur est toujours accessible dans son intégralité pour l'échantillonnage comme s'il était stocké sur un seul périphérique multiport. L'avantage est que les quatre périphériques REM à port unique occupent environ un tiers de moins de surface totale qu'un périphérique multiport.

"Nous avons essentiellement modifié la façon dont le vecteur est physiquement mappé dans la mémoire et modifié le flux de données, cette nouvelle cartographie peut donc être intégrée au processus d'échantillonnage. En utilisant ces astuces d'architecture, nous avons réduit la consommation d'énergie et la surface occupée, tout en maintenant le débit souhaité, " dit Banerjee.

Le circuit intègre également un petit composant de mémoire d'instructions qui peut être programmé avec des instructions personnalisées pour gérer différentes techniques d'échantillonnage, telles que des distributions de probabilité et des écarts types spécifiques, ainsi que différentes tailles et opérations vectorielles. Ceci est particulièrement utile, car les schémas de cryptographie basés sur le réseau changeront très probablement légèrement dans les années et décennies à venir.

Des paramètres réglables peuvent également être utilisés pour optimiser l'efficacité et la sécurité. Plus le calcul est complexe, plus l'efficacité est faible, et vice versa. Dans leur papier, les chercheurs détaillent comment naviguer dans ces compromis avec leurs paramètres réglables. Prochain, les chercheurs prévoient de peaufiner la puce pour exécuter tous les schémas de cryptographie basés sur le réseau répertoriés dans la deuxième phase du NIST.

Cette histoire est republiée avec l'aimable autorisation de MIT News (web.mit.edu/newsoffice/), un site populaire qui couvre l'actualité de la recherche du MIT, innovation et enseignement.