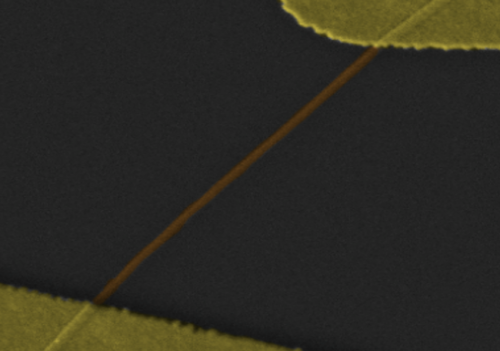

Un nanofil d'oxyde de titane agit à la fois comme une diode et un memristor

Chercheurs à AMBER, le centre de science des matériaux financé par la Science Foundation Ireland, et l'école de chimie, Trinity College Dublin, ont développé une solution pour augmenter la vitesse d'interaction entre le processeur et la mémoire dans les ordinateurs et autres appareils électroniques.

Au lieu que chaque cellule de mémoire ne stocke qu'un seul élément ou « bit » d'informations, l'équipe - dirigée par le professeur John Boland avec les chercheurs Curtis O'Kelly et Jessamyn Fairfield a développé une mémoire à plusieurs niveaux dans laquelle il est possible de programmer un certain nombre de bits stockés dans une seule cellule. La mémoire à plusieurs niveaux augmente la vitesse de communication en réduisant le nombre de cellules de mémoire.

Que votre application préférée fonctionne sur un téléphone mobile ou un superordinateur, les performances ne dépendent plus uniquement de la puissance du cerveau ou de la soi-disant vitesse du processeur. Pour fonctionner, le processeur doit communiquer efficacement avec la mémoire de la puce. Les propriétés des fils métalliques reliant le processeur et la mémoire fournissent une limite de vitesse fondamentale.

le professeur John Boland, AMBRE, a expliqué : « Les processeurs et la mémoire communiquent en utilisant le langage maladroit du code binaire. La mémoire conventionnelle sur puce stocke les informations sous forme de « 1 » et « 0 », qui reflète la présence ou l'absence de charge à l'emplacement mémoire. Par exemple, 2014 en langage binaire nécessite 11 cellules de mémoire. Il faut du temps à l'ordinateur pour accéder à un si grand nombre de cellules et donc les performances globales sont altérées. Le nouveau procédé réduit le nombre de cellules nécessaires. »

Le schéma proposé par les chercheurs d'AMBER fonctionne sur un principe différent; la résistance au flux de charge, connue sous le nom de mémoire résistive qui conduit finalement à un traitement plus rationalisé avec moins de cellules mais chacune ayant plusieurs niveaux de mémoire. Un avantage particulier de la nouvelle approche est qu'il est possible d'ajuster arbitrairement le nombre de niveaux de mémoire dans chaque cellule.

"La découverte ouvre une multitude de possibilités pour le consommateur conduisant à de plus petits, électronique moins chère et plus rapide. Ayant démontré six niveaux de mémoire par cellule, nous pensons que la technologie peut être développée pour afficher encore plus de niveaux de mémoire par cellule. Un langage de mémoire avec une plus grande densité peut augmenter l'efficacité et la vitesse de la technologie de bureau et mobile en réduisant le nombre d'emplacements de mémoire, " a déclaré le professeur Boland.

« Des recherches supplémentaires seront axées sur l'intégration de cette technologie aux capacités de fabrication existantes de l'industrie, afin que la société puisse continuer à récolter les bénéfices d'une technologie nouvelle et améliorée, " a conclu le professeur Boland.