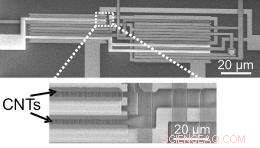

Une image au microscope électronique montrant des transistors à nanotubes de carbone (CNT) disposés dans un circuit logique intégré.

(PhysOrg.com) -- Les ingénieurs de Stanford ont construit ce qu'ils croient être une puce avec les éléments de calcul et de stockage les plus avancés à ce jour en nanotubes de carbone en concevant un moyen d'éliminer la complication tenace des nanotubes qui provoquent des courts-circuits.

Nanotubes, qui ressemblent à des pailles microscopiques de grillage enroulé, sont largement considérés comme la prochaine génération potentielle de matériaux permettant d'améliorer la vitesse et l'efficacité énergétique des puces informatiques.

Les chercheurs ont présenté leurs résultats aujourd'hui à l'International Electron Devices Meeting (IEDM) à Baltimore, avec une autre avancée dans l'utilisation de nanotubes pour fabriquer des multicouches, circuits tridimensionnels.

"Cet ensemble de travaux illustre que la technologie des transistors à nanotubes de carbone est passée au-delà du domaine de la découverte scientifique et dans la recherche en ingénierie, " a déclaré H.-S. Philip Wong, professeur de génie électrique à Stanford et co-auteur de l'article. « Nous sommes désormais en mesure de construire des appareils et des circuits à l'échelle d'une plaquette, par opposition aux précédentes démonstrations de type « unique en son genre ». Les appareils se trouvent dans un environnement de circuit qui répond aux besoins des systèmes d'aujourd'hui et de demain. »

La poignée de transistors à nanotubes dans les circuits fabriqués par l'équipe ne peut pas se comparer aux centaines de millions de transistors sur un microprocesseur commercial ou une puce mémoire, mais leur arrangement, la façon dont ils ont été fabriqués et leurs propriétés sont beaucoup plus proches de la qualité commerciale que tous les dispositifs à nanotubes fabriqués auparavant, dit Subhasish Mitra, professeur adjoint d'informatique et de génie électrique à Stanford.

Les transistors sont regroupés dans les mêmes séquences "en cascade" nécessaires pour produire la logique de calcul et la mémoire, et le procédé utilisé pour les fabriquer est compatible avec la norme de fabrication industrielle VLSI (Very Large Scale Integration).

« Nous sommes très heureux des progrès rapides réalisés par les professeurs Wong et Mitra et leurs équipes de recherche dans le développement de ces technologies pour aider à surmonter les obstacles à une intégration plus poussée de circuits électroniques complexes à base de carbone, qui conduiront à des produits plus utiles pour les générations futures, " a déclaré Betsy Weitzman, vice-président exécutif et directeur du programme de recherche du centre de recherche de Semiconductor Research Corporation, qui a aidé à financer la recherche, avec la National Science Foundation.

Les puces utilisent trois techniques avancées inventées à Stanford pour surmonter les problèmes endémiques associés aux nanotubes. Une, inventé en 2007, permet aux transistors de fonctionner indépendamment du fait que les nanotubes composants soient parfaitement droits. Un autre, inventé en 2008, permet la fabrication à l'échelle VLSI de transistors à nanotubes sur une puce. Celui annoncé aujourd'hui à l'IEDM, est un procédé permettant d'éliminer de manière fiable les nanotubes qui conduisent toujours le courant électrique même lorsqu'ils ne sont pas censés le faire. Ces nanotubes "métalliques" gênants peuvent court-circuiter les transistors s'ils ne sont pas retirés. La difficulté rencontrée par les chercheurs est de trouver des moyens d'éliminer tous les nanotubes gênants, sans endommager aucune autre partie d'un circuit, y compris les nanotubes qui se comportent correctement.

La nouvelle technique, que les chercheurs appellent l'élimination des nanotubes métalliques compatible VLSI (VMR), s'appuie sur une idée proposée pour la première fois par Paul Collins et ses collègues d'IBM en 2001. Cette idée était de briser les nanotubes en les exposant à un courant élevé. L'équipe de Stanford a maintenant rendu l'idée pratique à l'échelle VLSI en créant une grille d'électrodes qui élimine les nanotubes indésirables. Cette même grille d'électrodes peut ensuite être gravée pour produire n'importe quelle conception de circuit, y compris ceux qui utilisent les techniques développées par Stanford mentionnées ci-dessus.

L'auteur principal de l'article VMR présenté à l'IEDM est l'étudiant diplômé en génie électrique de Stanford, Nishant Patil. D'autres auteurs incluent les étudiants diplômés en génie électrique Albert Lin, Jie Zhang et Hai Wei, et l'étudiant de premier cycle Kyle Anderson.

Circuits de nanotubes 3D

Cinq membres de l'équipe (Wei, Patil, Lin, Wong et Mitra) ont immédiatement suivi l'article VMR à l'IEDM avec une autre présentation décrivant le premier circuit intégré tridimensionnel à nanotubes de carbone multicouches.

Comme les garages de stationnement à plusieurs niveaux, les circuits tridimensionnels permettent d'emballer plus d'unités - dans ce cas, transistors - dans une zone confinée. Sur des chips, la troisième dimension peut également réduire les longueurs de certains fils d'interconnexion, réduire l'énergie nécessaire à la transmission des données. Alors que les ingénieurs ont récemment commencé à faire des progrès dans la construction de circuits tridimensionnels en empilant et en connectant des couches fabriquées avec des matériaux conventionnels, le travail de Stanford montre que cela peut être fait avec des nanotubes d'une manière qui est intégrée dès le départ en tant que conception 3D, ce qui donne une plus grande densité de connexions entre les couches.

Indiquant que des progrès sont possibles avec les nanotubes, les chercheurs de Stanford ont pu fabriquer un prototype de puce à trois couches avec des dizaines de transistors à nanotubes connectés dans des portes logiques fonctionnelles par des nanotubes et un câblage métallique. Qu'est-ce qui a rendu l'exploit possible, Mitra a dit, était l'utilisation d'un processus à relativement basse température que les chercheurs ont développé l'année dernière dans lequel les nanotubes sont transférés d'une plaquette de quartz sur une puce de silicium.

Un défi restant est d'augmenter le nombre de nanotubes qui peuvent être correctement modelés sur une zone donnée d'une puce, pour permettre de fabriquer les millions de transistors dont les conceptions modernes ont besoin. Ce n'est pas un obstacle que les chercheurs s'attendent à ne pas franchir.

Les deux projets ont été soutenus par le Focus Center Research Program et la Direction de l'informatique et des sciences et de l'ingénierie de la National Science Foundation (CISE).

"NSF et en particulier le CISE, est très intéressé par l'exploration de nouvelles voies passionnantes pour obtenir des améliorations continues des performances matérielles au-delà des limites de la loi de Moore, " dit Sampath Kannan, un directeur de division CISE à la National Science Foundation.

"L'équipe dirigée par les professeurs Mitra et Wong, soutenu par plusieurs subventions du CISE, est une recherche pionnière dans l'une de ces avenues. Leurs nouveaux résultats sur la technique à l'échelle VLSI pour traiter les nanotubes de carbone métalliques pour la conception de circuits et leur démonstration expérimentale de circuits CNT compatibles VLSI immunisés contre les imperfections nous rapprochent de la réalisation pratique des circuits intégrés utilisant des nanotubes de carbone. »

Fourni par l'Université de Stanford (actualité :web)