Une nouvelle conception de puce photonique réduit considérablement l'énergie nécessaire pour calculer avec la lumière, avec des simulations suggérant qu'il pourrait exécuter des réseaux de neurones optiques 10 millions de fois plus efficacement que ses homologues électriques. Crédit :Nouvelles du MIT

Des chercheurs du MIT ont développé une nouvelle puce "photonique" qui utilise la lumière au lieu de l'électricité et consomme relativement peu d'énergie dans le processus. La puce pourrait être utilisée pour traiter des réseaux de neurones massifs des millions de fois plus efficacement que les ordinateurs classiques d'aujourd'hui.

Les réseaux de neurones sont des modèles d'apprentissage automatique largement utilisés pour des tâches telles que l'identification d'objets robotiques, traitement du langage naturel, développement de médicaments, l'imagerie médicale, et alimenter des voitures sans conducteur. Nouveaux réseaux de neurones optiques, qui utilisent des phénomènes optiques pour accélérer le calcul, peuvent fonctionner beaucoup plus rapidement et plus efficacement que leurs homologues électriques.

Mais à mesure que les réseaux de neurones traditionnels et optiques deviennent de plus en plus complexes, ils consomment des tonnes d'énergie. Pour s'attaquer à ce problème, chercheurs et grandes entreprises technologiques, y compris Google, IBM, et Tesla—ont développé des « accélérateurs d'IA, " puces spécialisées qui améliorent la vitesse et l'efficacité de la formation et du test des réseaux de neurones.

Pour les puces électriques, y compris la plupart des accélérateurs d'IA, il existe une limite théorique minimale de consommation d'énergie. Récemment, Des chercheurs du MIT ont commencé à développer des accélérateurs photoniques pour les réseaux de neurones optiques. Ces puces exécutent des ordres de grandeur plus efficacement, mais ils reposent sur des composants optiques encombrants qui limitent leur utilisation à des réseaux de neurones relativement petits.

Dans un article publié en Examen physique X , Les chercheurs du MIT décrivent un nouvel accélérateur photonique qui utilise des composants optiques plus compacts et des techniques de traitement du signal optique, pour réduire considérablement la consommation d'énergie et la surface de la puce. Cela permet à la puce de s'adapter aux réseaux de neurones de plusieurs ordres de grandeur plus grands que ses homologues.

La formation simulée de réseaux de neurones sur l'ensemble de données de classification d'images MNIST suggère que l'accélérateur peut théoriquement traiter les réseaux de neurones plus de 10 millions de fois en dessous de la limite de consommation d'énergie des accélérateurs électriques traditionnels et environ 1, 000 fois en dessous de la limite des accélérateurs photoniques. Les chercheurs travaillent actuellement sur un prototype de puce pour prouver expérimentalement les résultats.

"Les gens recherchent une technologie capable de calculer au-delà des limites fondamentales de la consommation d'énergie, " dit Ryan Hamerly, un post-doctorat au Laboratoire de Recherche en Electronique. « Les accélérateurs photoniques sont prometteurs… mais notre motivation est de construire un [accélérateur photonique] pouvant évoluer jusqu'à de grands réseaux de neurones. »

Les applications pratiques de ces technologies incluent la réduction de la consommation d'énergie dans les centres de données. « Il existe une demande croissante de centres de données pour l'exploitation de grands réseaux de neurones, et cela devient de plus en plus difficile à résoudre au fur et à mesure que la demande augmente, " dit le co-auteur Alexander Sludds, un étudiant diplômé du Laboratoire de recherche en électronique. L'objectif est de « répondre à la demande de calcul avec du matériel de réseau neuronal … pour remédier au goulot d'étranglement de la consommation d'énergie et de la latence ».

Rejoindre Sludds et Hamerly sur le papier sont :co-auteur Liane Bernstein, un étudiant diplômé RLE; Marin Soljacic, un professeur de physique au MIT; et Dirk Englund, professeur agrégé de génie électrique et d'informatique au MIT, un chercheur en RLE, et directeur du Laboratoire de photonique quantique.

Design compact

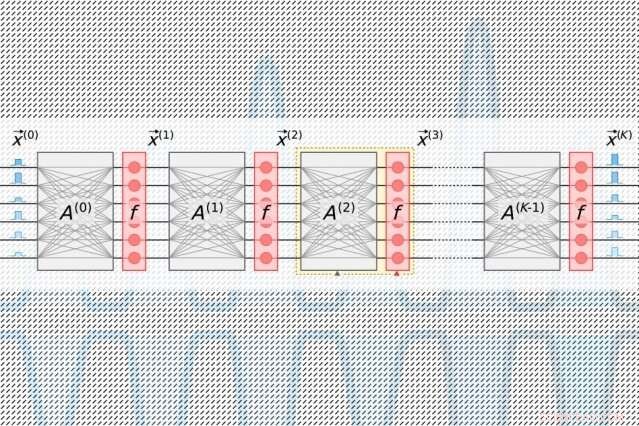

Les réseaux de neurones traitent les données à travers de nombreuses couches de calcul contenant des nœuds interconnectés, appelé "neurones", " pour trouver des modèles dans les données. Les neurones reçoivent une entrée de leurs voisins en amont et calculent un signal de sortie qui est envoyé aux neurones plus en aval. Chaque entrée se voit également attribuer un "poids, " une valeur basée sur son importance relative par rapport à toutes les autres entrées. Au fur et à mesure que les données se propagent " plus profondément " à travers les couches, le réseau apprend progressivement des informations de plus en plus complexes. À la fin, une couche de sortie génère une prédiction basée sur les calculs dans toutes les couches.

Tous les accélérateurs d'IA visent à réduire l'énergie nécessaire pour traiter et déplacer les données lors d'une étape d'algèbre linéaire spécifique dans les réseaux de neurones, appelé "multiplication matricielle". Là, les neurones et les poids sont codés dans des tableaux séparés de lignes et de colonnes, puis combinés pour calculer les sorties.

Dans les accélérateurs photoniques traditionnels, des lasers pulsés codés avec des informations sur chaque neurone d'une couche circulent dans des guides d'ondes et à travers des séparateurs de faisceau. Les signaux optiques résultants sont introduits dans une grille de composants optiques carrés, appelés "interféromètres de Mach-Zehnder, " qui sont programmés pour effectuer des multiplications matricielles. Les interféromètres, qui sont codés avec des informations sur chaque poids, utiliser des techniques d'interférence de signal qui traitent les signaux optiques et les valeurs de poids pour calculer une sortie pour chaque neurone. Mais il y a un problème d'échelle :pour chaque neurone, il doit y avoir un guide d'ondes et, pour chaque poids, il doit y avoir un interféromètre. Parce que le nombre de poids correspond au nombre de neurones, ces interféromètres occupent beaucoup d'espace.

"Vous réalisez rapidement que le nombre de neurones d'entrée ne peut jamais être supérieur à 100 environ, parce que vous ne pouvez pas installer autant de composants sur la puce, " dit Hamerly. " Si votre accélérateur photonique ne peut pas traiter plus de 100 neurones par couche, alors il est difficile d'implémenter de grands réseaux de neurones dans cette architecture."

La puce des chercheurs repose sur un boîtier plus compact, schéma "optoélectronique" économe en énergie qui encode les données avec des signaux optiques, mais utilise la "détection homodyne équilibrée" pour la multiplication matricielle. C'est une technique qui produit un signal électrique mesurable après avoir calculé le produit des amplitudes (hauteurs d'onde) de deux signaux optiques.

Des impulsions de lumière codées avec des informations sur les neurones d'entrée et de sortie pour chaque couche de réseau neuronal, qui sont nécessaires pour entraîner le réseau, circulent à travers un seul canal. Des impulsions séparées codées avec des informations de rangées entières de poids dans la table de multiplication matricielle circulent à travers des canaux séparés. Les signaux optiques transportant le neurone et les données de poids se diffusent vers une grille de photodétecteurs homodynes. Les photodétecteurs utilisent l'amplitude des signaux pour calculer une valeur de sortie pour chaque neurone. Chaque détecteur alimente un signal de sortie électrique pour chaque neurone dans un modulateur, qui reconvertit le signal en une impulsion lumineuse. Ce signal optique devient l'entrée de la couche suivante, etc.

La conception ne nécessite qu'un seul canal par neurone d'entrée et de sortie, et seulement autant de photodétecteurs homodynes qu'il y a de neurones, pas de poids. Parce qu'il y a toujours beaucoup moins de neurones que de poids, cela permet un gain de place important, la puce est donc capable de s'adapter aux réseaux de neurones avec plus d'un million de neurones par couche.

Trouver le bon endroit

Avec des accélérateurs photoniques, il y a un bruit inévitable dans le signal. Plus la lumière est introduite dans la puce, moins il y a de bruit et plus la précision est grande, mais cela devient assez inefficace. Moins de lumière d'entrée augmente l'efficacité mais a un impact négatif sur les performances du réseau neuronal. Mais il y a un « endroit idéal, " dit Bernstein, qui utilise une puissance optique minimale tout en maintenant la précision.

Ce point idéal pour les accélérateurs d'IA est mesuré en combien de joules il faut pour effectuer une seule opération de multiplication de deux nombres, comme lors de la multiplication matricielle. À l'heure actuelle, les accélérateurs traditionnels se mesurent en picojoules, ou un billionième de joule. Les accélérateurs photoniques mesurent en attojoules, ce qui est un million de fois plus efficace.

Dans leurs simulations, les chercheurs ont découvert que leur accélérateur photonique pouvait fonctionner avec une efficacité inférieure à l'attojoule. "Il y a une puissance optique minimale que vous pouvez envoyer, avant de perdre en précision. La limite fondamentale de notre puce est bien inférieure aux accélérateurs traditionnels… et inférieure aux autres accélérateurs photoniques, " dit Bernstein.

Cette histoire est republiée avec l'aimable autorisation de MIT News (web.mit.edu/newsoffice/), un site populaire qui couvre l'actualité de la recherche du MIT, innovation et enseignement.