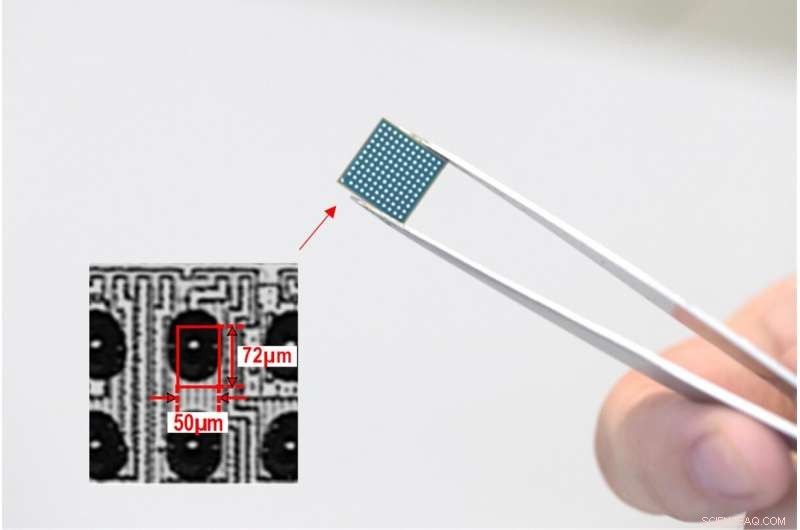

L'ensemble de la PLL entièrement numérique tient dans une région de 50 × 72 m2, ce qui en fait la plus petite PLL à ce jour. Crédit :Kenichi Okada

Des scientifiques de l'Institut de technologie de Tokyo (Tokyo Tech) et de Socionext Inc. ont conçu la plus petite boucle à verrouillage de phase (PLL) entièrement numérique au monde. Les PLL sont des circuits d'horloge critiques dans pratiquement toutes les applications numériques, et réduire leur taille et améliorer leurs performances est une étape nécessaire pour permettre le développement de technologies de nouvelle génération.

Technologies nouvelles ou améliorées, comme l'intelligence artificielle, Communications cellulaires 5G, et l'Internet des objets, devraient apporter des changements révolutionnaires dans la société. Mais pour que cela se produise, Les systèmes sur puce (SoC) hautes performances, un type de circuit intégré, sont indispensables. Un élément de base des dispositifs SoC est la boucle à verrouillage de phase (PLL), un circuit qui se synchronise avec la fréquence d'une oscillation de référence et émet un signal avec la même fréquence ou une fréquence supérieure. Les PLL génèrent des "signaux de synchronisation, ' dont les oscillations agissent comme un métronome qui fournit une référence temporelle précise pour le fonctionnement harmonieux des appareils numériques.

Pour réaliser des dispositifs SoC hautes performances, les procédés de fabrication de l'électronique à semi-conducteurs doivent devenir plus sophistiqués. Plus la zone de mise en œuvre des circuits numériques est petite, meilleures sont les performances de l'appareil. Les fabricants se sont précipités pour développer des semi-conducteurs de plus en plus petits. Les semi-conducteurs 7 nm (une amélioration considérable par rapport à leur prédécesseur 10 nm) sont déjà en production, et les méthodes pour construire ceux de 5 nm sont actuellement à l'étude.

Cependant, dans cette entreprise se dresse un goulot d'étranglement majeur. Les PLL existantes nécessitent des composants analogiques, qui sont généralement encombrants et ont des conceptions difficiles à réduire.

Des scientifiques de Tokyo Tech et Socionext Inc., dirigé par le professeur Kenichi Okada, ont résolu ce problème en implémentant une PLL fractionnaire « synthétisable », qui ne nécessite que des portes logiques numériques, et pas de composants analogiques encombrants, le rendant facile à adopter dans les circuits intégrés miniaturisés classiques.

Okada et son équipe ont utilisé plusieurs techniques pour réduire la surface requise, la consommation d'énergie et la gigue (fluctuations temporelles indésirables lors de la transmission de signaux numériques) de leurs PLL synthétisables. Pour diminuer la surface, ils ont utilisé un oscillateur en anneau, un oscillateur compact qui peut être facilement réduit. Pour supprimer la gigue, ils ont réduit le bruit de phase - les fluctuations aléatoires d'un signal - de cet oscillateur en anneau, en utilisant le « verrouillage par injection » - le processus de synchronisation d'un oscillateur avec un signal externe dont la fréquence (ou un multiple de celle-ci) est proche de celle de l'oscillateur - sur une large gamme de fréquences. Le bruit de phase inférieur, à son tour, consommation d'énergie réduite.

La conception de cette PLL synthétisable surpasse celle de toutes les autres PLL de pointe actuelles dans de nombreux aspects importants. Il atteint les meilleures performances de gigue avec la consommation d'énergie la plus faible et la plus petite surface (comme le montre la figure 1). « La zone centrale est de 0,0036 mm2, et l'ensemble de la PLL est implémenté comme une seule configuration avec une seule alimentation, " remarque Okada. De plus, il peut être construit à l'aide d'outils de conception numérique standard, permettant sa rapidité, à faible effort, et une production à faible coût, le rendant commercialement viable.

Cette PLL synthétisable s'intègre facilement dans la conception de SoC tout numériques, et est commercialement viable, ce qui le rend précieux pour le développement du très recherché semi-conducteur 5 nm pour des applications de pointe, notamment l'intelligence artificielle, internet des objets et bien d'autres, où des performances élevées et une faible consommation d'énergie seraient les exigences critiques. Mais les apports de cette recherche vont au-delà de ces possibilités. "Notre travail démontre le potentiel des circuits synthétisables. Avec la méthodologie de conception employée ici, d'autres blocs de construction de SoC, tels que les convertisseurs de données, circuits de gestion de l'alimentation, et émetteurs-récepteurs sans fil, pourrait également être rendu synthétisable. Cela augmenterait considérablement la productivité de la conception et réduirait considérablement les efforts de conception, " explique Okada. Tokyo Tech et Socionext poursuivront leur collaboration dans ce domaine pour faire avancer la miniaturisation des appareils électroniques, permettant la réalisation de technologies de nouvelle génération.