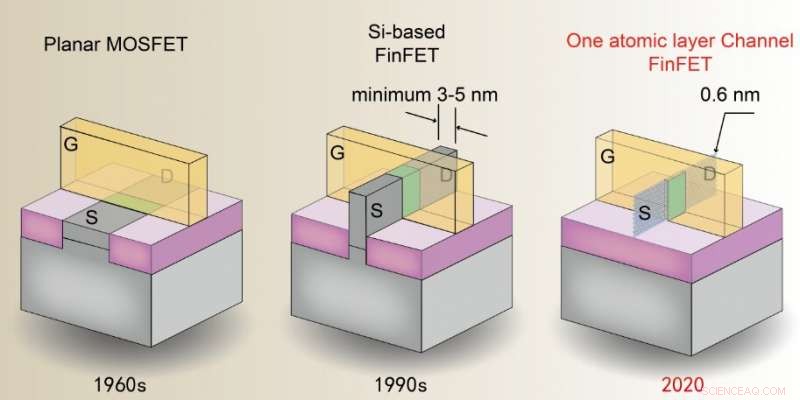

Différentes configurations de MOSFET. Crédit :IMR

Les FinFET sont connus pour être une évolution des transistors à effet de champ métal-oxyde-semiconducteur (MOSFET) comportant un canal semi-conducteur enveloppé verticalement par des électrodes de grille conformes. Il a été proposé pour la première fois dans les années 1990 afin d'éviter l'effet de canal court et d'autres inconvénients résultant de la réduction de la taille des transistors. En raison de la limitation de la nanofabrication, la largeur minimale des ailettes est d'environ 5 nm dans la technologie actuelle.

Au cours des dernières décennies, la microélectronique s'est développée à un rythme rapide suivant la loi de Moore, avec le nombre de transistors par zone augmenté tous les deux ans. En raison de la limitation de la précision de la nano-fabrication, il est maintenant extrêmement difficile de réduire davantage la taille des transistors sur un circuit intégré. Il est donc très important de rechercher de nouveaux candidats de matériaux semi-conducteurs.

Dans les années récentes, de nouveaux matériaux tels que les nanotubes de carbone et les matériaux bidimensionnels (2-D) ont été largement étudiés pour la mise en œuvre de transistors à l'échelle nanométrique. Dans une nouvelle étude publiée dans Communication Nature , les chercheurs de l'Institute of Metal Research (IMR) de l'Académie chinoise des sciences et de la France visaient à remplacer l'ailette conventionnelle à base de Si par une couche atomique unique 2D dans l'architecture FinFET.

Les chercheurs ont conçu une méthode de dépôt chimique en phase vapeur (CVD) par pulvérisation humide pour faire croître de manière universelle des monocouches de dichalcogénures de métaux de transition (ML-TMDC, comme le MoS

Après un flux de travail dédié de processus de gravure en plusieurs étapes et de nanofabrication, MoS monocouche vertical

Les meilleures performances électriques de ces ML-FinFET ont été obtenues pour montrer un rapport marche/arrêt atteignant 10 7 , oscillation sous le seuil d'environ 300 mV/déc, et des mobilités de l'ordre de quelques cm 2 V -1 s -1 . Les simulations ont montré qu'en optimisant davantage la structure des ML-FinFET, L'abaissement de la barrière induite par le drain (DIBL) peut être abaissé à 5 mV/V.

Cette étude a réalisé un FinFET avec une largeur d'aileron inférieure à 1 nm via une voie ascendante pour cultiver du MoS monocouche (ML)